超深亚微米设计中串扰的影响及避免

分析了在超深亚微米阶段,串扰对高性能芯片设计的影响,介绍了消除串扰影响的方法。

关键词:串扰,布线,关键路径,超深亚微米

在超深亚微米阶段(0.18μm以下),如何保证信号的完整越来越重要,而由信号完整性引起的逻辑和时序问题,常使芯片不能实现时序的正确收敛,或在测试过程中不能正常工作。串扰就是最常见的信号完整性问题。当两个或两个以上的布线路径存在一定距离并呈并行分布时,彼此之间就存在把脉冲从一个节点传到另一个节点的耦合电容(Coupling Capacitance),串扰由此而来。

随着每次超深亚微米(Ultra Deep Sub Micron,UDSM)新工艺技术的出现,特性尺寸、线宽和线间距都将进一步缩小,设计人员都想在裸片保持不变的情况下,把更多功能挤进片上系统中,这无疑将大大增加布线的复杂度,使得线路更加拥挤。由于金属阻抗与其宽度成反比,为追求更小的阻抗,金属线的厚度不断地增加,层数也不断增加,且金属线的长度比以往更长。这种趋势导致金属之间的交叉耦合电容增加。另外,由于芯片上叠加了更多的金属层,高金属层与基底层之间的距离加大,从而减小了对地的电容量,从而使金属线之间交叉耦合电容的比重不断上升,串扰效应对复杂数字电路的影响也越来越大。

当串扰产生的噪声传输到一个锁存器(触发器、寄存器)的输入,会引起逻辑的异常改变而导致逻辑运算出错。但串扰产生的噪声一般不成为问题。通过分析各个单元的噪声传输模型,可使必须要有额外间距的串扰敏感网络的数量减少。噪声传输模型在输入波形的基础上定义了输出波形的峰值与宽度,如果输入波形的峰值和宽度小于分析所确定的门限值,那么,噪声就无法通过该单元。

依据攻击网和受害网的信号传输方向,串扰对时延的影响可分为以下两种:(1)两者传输方向相反,会导致受害网时延增加。(2)两者传输方向相同,会导致受害网时延减少。

串扰对时序的影响,将导致高速芯片不能以最快速度工作。因为“受害”网的时序是通过门电路的时延、相互连接的延迟以及相邻网的状态决定的,因此,由串扰产生的时序问题微妙而复杂。每个周期都存在延迟,而不仅仅是互连引起的延迟,这些延迟的变化会造成时序无法收敛。

要准确说明串扰对延迟的影响,设计人员需要特殊技术来处理UDSM设计中的大量寄生数据,如攻击信号和受害信号之间复杂的时序和逻辑关系等。分析串扰引起的延迟首先从确认潜在受害信号网络开始。通过高级互连分析技术,串扰分析工具可对设计进行分析,找出干扰噪声超过规定限度的网络。接着,计算每个受害网络的典型延迟,同时,所有可能的攻击网络保持静止状态;然后,串扰分析工具将攻击网络的方向转换为与受害网络相反,计算出受害网络最大延迟增加量,最后再将攻击网方向转换为与受害网相同,计算最大延迟减少量。

2 串扰避免(Crosstalk Avoidance)

串扰分析完毕后,就需要对其进行处理,典型的方法包括加入缓冲、重新设计单元、对受害网重新进行布线。一般情况下不采用插入缓冲器的方法,因为它会引入额外的时延,可能会在关键路径(最大或最小时延路径)引起时序错误,而且它还会增加总的芯片功率;重新布线,简单讲就是将金属线从一处移至另一处,这样就可以将经分析已知的串扰问题解决,然而由于金属线的移动,可能会在别处产生新的串扰问题及关键路径;重新设计单元是最为有效的方法,因为被替换的单元对于整个版图设计来讲,仅有局部的影响,在与周围的单元连接时,只需要对准各个信号接口即可。

目前,布线后再进行串扰分析的做法已经无法满足设计要求。从复杂的布局到具体的布线,都要求在设计的各个阶段开展信号完整性分析。设计工程师使用不同工具时应全面考虑信号完整性、时序、功率和芯片面积等问题。当出现串扰问题时,这些工具必须能确定解决串扰问题的自动化设计方法,同时不影响其它设计参数。

2.1 整体布局

任何解决串扰问题的有效方法都包括对串扰的预测,从而在设计的初期就注意减少串扰的发生。对于那些无法避免串扰的线路要进行修改,尽量减少串扰。

在整体布局阶段,通过串扰敏感静态时序分析工具,对关键路径上串扰所能造成的影响进行估计。由于在布局阶段,信号间的连接情况及布线结构存在着不确定性,因此,很难准确判断还未具体布线的金属线之间的串扰效应。但如果具体布线时按照全局设想的那样进行,则对串扰的估计就相当准确。然而,现有的布线技术还不能保证具体的布线工具能按照全局布线器所指定的路径进行布线,且保证连接良好。对于那些布线面积很小的高性能设计来说,这种限制更加明显,其最终结果是全局布线阶段所进行的串扰分析失效。

一个实际的方法是全局布线器将各个信号网分配到全局布线单元,这些单元以各层可用空间为边界,然后根据布线规则完成各个单元的布线,以及单元之间的信号连接。使用统计学的方法,各个单元间的耦合效应可以被估计出来,然后再使用静态时序分析工具,决定单元中哪些信号网处于关键路径中。一旦串扰敏感网络被确定,就可以使用额外的布线空间来降低串扰。

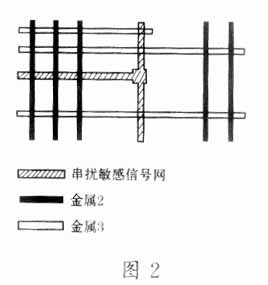

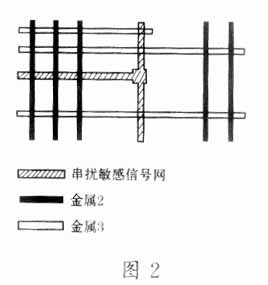

如图2所示,串扰敏感信号网跨接了两个金属层,所以在两金属层中分别加宽其与同层金属线的间距,这样即可减轻串扰的影响。

2.2 合理确定间距

对于在整体布局阶段被预测到的串扰,可采取多种措施来降低其影响。一个最简单实效的方法是加大间距。测试表明,如果一个信号网一边的间距增大一倍,串扰效应就可减轻一半。如果信号网两边的间距都增大一倍,则串扰可减轻3/4。

然而,布线资源是非常有限的,要在有限的面积中完成要求的功能并避免串扰,对于设计者来说是非常大的挑战,且设计者必须注意,间距首先应符合设计规则,这是由生产工艺所决定的。在具体布线时,只有在满足规则的基础上,才能考虑使用增加空间间距的方法来降低串扰。所以,在设计中要做到合理确定间距,设计者不仅要使用在布局及布线中能解决问题的工具,更需要平时在设计中不断积累实践经验。

由于现有的工具还不能在布局阶段解决所有的串扰问题,再加上布线的复杂性及不确定性,仍有必要在布线后对串扰进行分析。但需要注意,布线后的校正操作要十分谨慎,否则会引发更多问题。最新的布局和布线工具支持布线后插入缓冲器及加入其它修复措施,把对其它节点的影响降到最小程度,但如果你的布线工具不具备这个功能,布线中试图解决串扰反而会引起新的问题。

3 结束语

及早解决由串扰引起的对逻辑功能和时序的影响,对于今后设计更高性能的芯片十分有益。从这一点来讲,设计中加入串扰避免的方法是极有必要的。

关键词:串扰,布线,关键路径,超深亚微米

在超深亚微米阶段(0.18μm以下),如何保证信号的完整越来越重要,而由信号完整性引起的逻辑和时序问题,常使芯片不能实现时序的正确收敛,或在测试过程中不能正常工作。串扰就是最常见的信号完整性问题。当两个或两个以上的布线路径存在一定距离并呈并行分布时,彼此之间就存在把脉冲从一个节点传到另一个节点的耦合电容(Coupling Capacitance),串扰由此而来。

随着每次超深亚微米(Ultra Deep Sub Micron,UDSM)新工艺技术的出现,特性尺寸、线宽和线间距都将进一步缩小,设计人员都想在裸片保持不变的情况下,把更多功能挤进片上系统中,这无疑将大大增加布线的复杂度,使得线路更加拥挤。由于金属阻抗与其宽度成反比,为追求更小的阻抗,金属线的厚度不断地增加,层数也不断增加,且金属线的长度比以往更长。这种趋势导致金属之间的交叉耦合电容增加。另外,由于芯片上叠加了更多的金属层,高金属层与基底层之间的距离加大,从而减小了对地的电容量,从而使金属线之间交叉耦合电容的比重不断上升,串扰效应对复杂数字电路的影响也越来越大。

1 串扰效应(Crosstalk Effect)

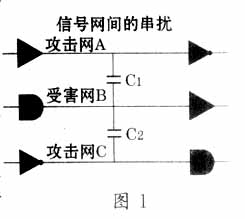

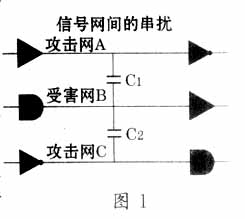

图1所示电路包含了三个信号网(A,B,C),它们间通过电容C1,C2耦合。

为了便于说明,先定义“攻击”网(Aggressor)和“受害”网(Victim):由于自身的逻辑电平发生变化,通过电容耦合而对其他信号产生影响的信号网称为“攻击”网。受到影响而导致自身逻辑电平发生异常的信号网称为“受害”网。

如果一个“攻击”节网信号发生变化,可导致邻近的“受害”网瞬态呈现一个异常的逻辑值,即噪声。对于每个信号网来说,可能存在多个攻击信号网,电路分析时,如果将各个攻击网都考虑进去,则必然要消耗大量的时间和计算资源。因此,通常串扰分析工具将各个攻击网的噪声峰值统加起来后,再应用到受害网(对受害网来说,这属于最坏情况)。

当串扰产生的噪声传输到一个锁存器(触发器、寄存器)的输入,会引起逻辑的异常改变而导致逻辑运算出错。但串扰产生的噪声一般不成为问题。通过分析各个单元的噪声传输模型,可使必须要有额外间距的串扰敏感网络的数量减少。噪声传输模型在输入波形的基础上定义了输出波形的峰值与宽度,如果输入波形的峰值和宽度小于分析所确定的门限值,那么,噪声就无法通过该单元。

依据攻击网和受害网的信号传输方向,串扰对时延的影响可分为以下两种:(1)两者传输方向相反,会导致受害网时延增加。(2)两者传输方向相同,会导致受害网时延减少。

串扰对时序的影响,将导致高速芯片不能以最快速度工作。因为“受害”网的时序是通过门电路的时延、相互连接的延迟以及相邻网的状态决定的,因此,由串扰产生的时序问题微妙而复杂。每个周期都存在延迟,而不仅仅是互连引起的延迟,这些延迟的变化会造成时序无法收敛。

要准确说明串扰对延迟的影响,设计人员需要特殊技术来处理UDSM设计中的大量寄生数据,如攻击信号和受害信号之间复杂的时序和逻辑关系等。分析串扰引起的延迟首先从确认潜在受害信号网络开始。通过高级互连分析技术,串扰分析工具可对设计进行分析,找出干扰噪声超过规定限度的网络。接着,计算每个受害网络的典型延迟,同时,所有可能的攻击网络保持静止状态;然后,串扰分析工具将攻击网络的方向转换为与受害网络相反,计算出受害网络最大延迟增加量,最后再将攻击网方向转换为与受害网相同,计算最大延迟减少量。

2 串扰避免(Crosstalk Avoidance)

串扰分析完毕后,就需要对其进行处理,典型的方法包括加入缓冲、重新设计单元、对受害网重新进行布线。一般情况下不采用插入缓冲器的方法,因为它会引入额外的时延,可能会在关键路径(最大或最小时延路径)引起时序错误,而且它还会增加总的芯片功率;重新布线,简单讲就是将金属线从一处移至另一处,这样就可以将经分析已知的串扰问题解决,然而由于金属线的移动,可能会在别处产生新的串扰问题及关键路径;重新设计单元是最为有效的方法,因为被替换的单元对于整个版图设计来讲,仅有局部的影响,在与周围的单元连接时,只需要对准各个信号接口即可。

目前,布线后再进行串扰分析的做法已经无法满足设计要求。从复杂的布局到具体的布线,都要求在设计的各个阶段开展信号完整性分析。设计工程师使用不同工具时应全面考虑信号完整性、时序、功率和芯片面积等问题。当出现串扰问题时,这些工具必须能确定解决串扰问题的自动化设计方法,同时不影响其它设计参数。

2.1 整体布局

任何解决串扰问题的有效方法都包括对串扰的预测,从而在设计的初期就注意减少串扰的发生。对于那些无法避免串扰的线路要进行修改,尽量减少串扰。

在整体布局阶段,通过串扰敏感静态时序分析工具,对关键路径上串扰所能造成的影响进行估计。由于在布局阶段,信号间的连接情况及布线结构存在着不确定性,因此,很难准确判断还未具体布线的金属线之间的串扰效应。但如果具体布线时按照全局设想的那样进行,则对串扰的估计就相当准确。然而,现有的布线技术还不能保证具体的布线工具能按照全局布线器所指定的路径进行布线,且保证连接良好。对于那些布线面积很小的高性能设计来说,这种限制更加明显,其最终结果是全局布线阶段所进行的串扰分析失效。

一个实际的方法是全局布线器将各个信号网分配到全局布线单元,这些单元以各层可用空间为边界,然后根据布线规则完成各个单元的布线,以及单元之间的信号连接。使用统计学的方法,各个单元间的耦合效应可以被估计出来,然后再使用静态时序分析工具,决定单元中哪些信号网处于关键路径中。一旦串扰敏感网络被确定,就可以使用额外的布线空间来降低串扰。

如图2所示,串扰敏感信号网跨接了两个金属层,所以在两金属层中分别加宽其与同层金属线的间距,这样即可减轻串扰的影响。

2.2 合理确定间距

对于在整体布局阶段被预测到的串扰,可采取多种措施来降低其影响。一个最简单实效的方法是加大间距。测试表明,如果一个信号网一边的间距增大一倍,串扰效应就可减轻一半。如果信号网两边的间距都增大一倍,则串扰可减轻3/4。

由于现有的工具还不能在布局阶段解决所有的串扰问题,再加上布线的复杂性及不确定性,仍有必要在布线后对串扰进行分析。但需要注意,布线后的校正操作要十分谨慎,否则会引发更多问题。最新的布局和布线工具支持布线后插入缓冲器及加入其它修复措施,把对其它节点的影响降到最小程度,但如果你的布线工具不具备这个功能,布线中试图解决串扰反而会引起新的问题。

3 结束语

及早解决由串扰引起的对逻辑功能和时序的影响,对于今后设计更高性能的芯片十分有益。从这一点来讲,设计中加入串扰避免的方法是极有必要的。

评论