高速低相位噪声VCO设计

关键词:压控振荡器,相位噪声,振荡频率

1 引 言

压控振荡器(Voltage Controlled Oscillator,VCO)已经成为当今时钟恢复电路和频率合成电路中不可缺少的组成部分。而在大部分无线通讯接收器中,高速、低相位噪声是VCO设计的最重要的指标。

本文分别从压控振荡器的振荡频率和相位噪声两个角度,详细阐述影响VCO性能的因素,并提出相应的改进方法。

在第2部分,将介绍一般VCO的设计方法,第3部分分析提高VCO振荡频率的方法,第4部分着重分析降低电路的相位噪声方法。文章最后给出在TSMC0.35工艺下仿真出的结果。

2 一般VCO的设计

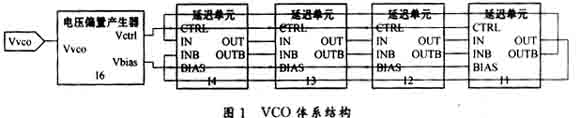

一般的VCO的体系结构如图1所示,由电压偏置产生器(voltage bias generator)和延迟单元(delaycell)两个部分组成。

电压偏置产生器为延迟单元产生偏置电压,延迟单元控制电压随着输入电压Vvco的改变而改变。设每个延迟单元的时间为tD,则振荡频率为固定的值:

F=1/(2NtD)(1)

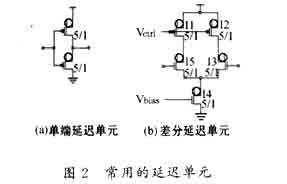

其中,N为VCO的延迟单元的数量。可见,延迟单元的数量能影响VCO的振荡频率。每个延迟单元的设计有很大的灵活性,常用的延迟单元如图2所示。

每种不同延迟单元可以根据振荡频率和相位噪声的要求做不同的改动。下面我们将详细讨论。

3 VCO振荡频率分析

由公式(1)可以看出,VCO的振荡频率与振荡回路的延迟单元的数量以及每个延迟单元的延迟时间成反比,所以,提高VCO的振荡频率无非就是要减少延迟单元的数量和每个延迟单元时间。但是延迟单元的数量并不是越少越好,因为,对于振荡回路来说,必须要满足振荡相位条件∠H(jωo)=180°,所以,延迟单元数量将受到单个延迟单元传输函数的约束。对于每个振荡单元延迟时间,以差分延迟单元为例进行分析。差分延迟单元的小信号模型如图3所示。

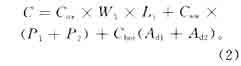

其中,R为负载的等效电阻,C为输出节点的总的电容。从小信号模型可以看出,电路延迟时间就是电流对输出节点的RC电路进行充电的时间,所以,减少单位延迟时间的方法有以下几种:(1)提高电路的静态电流;(2)减少负载管的等效电阻;(3)减少输出节点的电容值。

提高电路的静态电流虽然提高了振荡频率,但是也大大增加了电路功耗。由于NMOS的电子漂移率要大于PMOS,所以,面积大小相同的条件下,NMOS的电阻要小于PMOS的电阻,这就为我们提供了一条提高振荡频率的方法。NMOS负载差分延迟单元如图4所示。

可见,采用多个并联结构后,两个MOS管会共用一个漏极,这样,总的漏极的面积会有所减少。如果版图采用环形的结构,寄生电容会更小。

4 VCO相位噪声分析

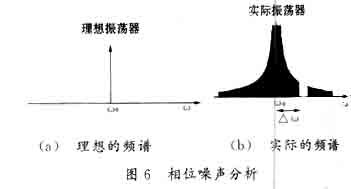

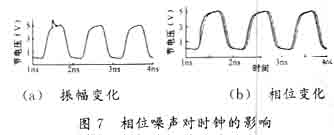

相位噪声分析通常是利用频谱分析。设,理想的振荡电路的中心频率为F0,该频谱上为位于F0上的一个脉冲。然而,在实际环境中,频谱往往有一带宽为△f的成分附在F0的周围。如图6所示。

相位噪声的来源可以归纳为以下几个部分:(1)负载管的热噪声;(2)电流沉噪声;(3)输入端口的白噪声;(4)电源噪声和衬底噪声。

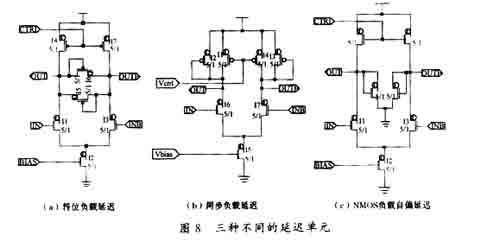

根据Hajimiri的噪声模型〔1〕,负载电容是与相位噪声相关不大的参数,增加静态电流能,增加负载电阻都能改善相位噪声。然而,在实际设计中,静态电流由于功耗的问题,不可能很大。而增加负载电阻又降低了振荡频率。所以,负载电容是设计的关键。实际设计中,通过改变单位延迟单元的结构,可以达到改善相位噪声的目的,图8给出了3种不同的延迟单元。

图8中,(a)、(b)两种延迟单元的噪声特性在参考文献2和3中分别给予了讨论。图8中(c)给出了一种低延迟时间及低相位噪声的延迟单元,它结合了图4和图8(b)的优点,利用自偏结构降低相位噪声,并采用比较节省寄生电容的NMOS负载,这样,就达到高速低相位噪声的设计目的。下面,将给出这种结构的仿真结果。

5 仿真结果

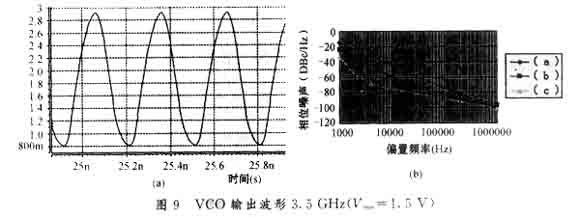

采用NMOS负载自偏结构的延迟单元,在TSMC0.35-3.3 V工艺库条件下得到比较理想的仿真结果,图9所示是VCO输出波形3.5 GHz(Vvco=1.5 V)。

当Vvco达到3 V时,振荡频率可以达到4.5 GHz~5 GHz,可见,这种延迟单元在高速时钟领域是很有实用价值的。图9(b)显示了该延迟单元和其他两种的相位噪声的对比图。结果也显示了该结构能较好地抑制相位噪声。

6 结束语

本文从振荡频率和相位噪声两个方面探讨了VCO的设计过程,并提出了一种有较好性能的延迟单元。实验证明,这种VCO结构能广泛地应用到要求高速低相位噪声的通讯领域中去。

2 M Horowitz,et al..PLL Design for a 500MB/s Interface.Int′lSolid-State Circuits Conference Digest,Feb.1993:160~161

3 JManeatis.Low-Jitter and Process-Independent DLLandPLL Based on Self-Biased Techniques.Int′l Solid-State Circuits Conference Digest,Feb.1996:130~131,430

评论