模拟视频监控采集电路设计—电路图天天读(300)

该系统可以完成图像的采集、处理和显示,从而实现目标识别与跟踪的智能信号处理。该系统是对摄像机数字,模拟两路视频数据进行采集,处理后通过PCI总线在PC机上显示出来。

视频信号采集模块

摄像机提供两路视频信号:一路模拟视频,一路数字视频。

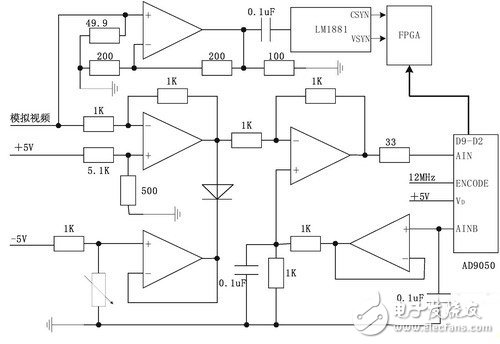

模拟视频信号经过钳位校正、放大后,将信号送入到A/D转换器,再经FPGA锁存后将视频信号发送给DSP1;经视频同步分离电路,由LM1881分离出模拟视频的行、场同步信号,用于控制视频数据采集到DSP1,以便进行图像处理。钳位校正、视频同步电路如图1所示。模拟视频经运放输入,将中心电平调到3.3V,加到 A/D输入端。A/D转换后的数据进入FPGA锁存。运放均采用ADI公司的AD8047AR,A/D转换器采用ADI公司的AD9050。AD9050 为10位A/D转换器,取其高8位进入FPGA。采样时钟12MHz,与数字视频信号相同。由FPGA对48MHz时钟四分频产生。

图1 模拟视频输入转换电路

摄像机的数字视频信号为14对差分信号,经FPGA将差分信号转换为单端信号,并锁存数据。每个象素14位,每帧320×240。

FPGA采用ALTERA公司的CYCLONE系列EP1C3T144C-6,配置芯片采用EPC2LC20。EP1C3T144C-6具有将差分信号转单端信号的专用I/O口。锁存在FPGA的数字,模拟两路视频信号根据工作模式选择输出到DSP1数据总线上,由DSP1读入处理,数据速率与模拟视频的采样速率,数字视频的数据速率相同。工作模式选择,开关控制通过PIC9054引入到FPGA。

DSP处理器模块

DSP处理器阵列模块主要由4片高速高性能的DSP处理芯片ADSP-TS201S组成多DSP处理器系统,ADSP-TS201S性能如下:

基本性能指标如下:

● 600MHz运行速度时,内核指令周期1.67ns

● 24M bits片上DRAM,分为6个4M bits块(128K words X 32 bits)

● 片内双运算模块,每个都包含一个ALU、一个乘法器、一个移位器和一个寄存器组

● 双整数ALU提供数据寻址和指针操作功能

● 片内提供14通道DMA、外部口、4个链路口、SDRAM控制器、可编程标志引脚、2个定时器

● 片上仲裁系统可实现8个TigerSHARC DSP的无缝连接

● 内部3条互相独立的128位总线

● 外部数据总线64位,地址总线32位

● 每秒48亿次40位宽的MAC运算或每秒12亿次80位宽的MAC运算;1024点复数FFT(基2)时间15.7us

● 外部端口 1G字节每秒;链路口(每个)1G字节每秒

DSP处理器阵列模块中DSP1是用来整理所收集到的视频信号,并进行相应的预处理后,将数据分发送到后面的DSP,进行进一步的处理。

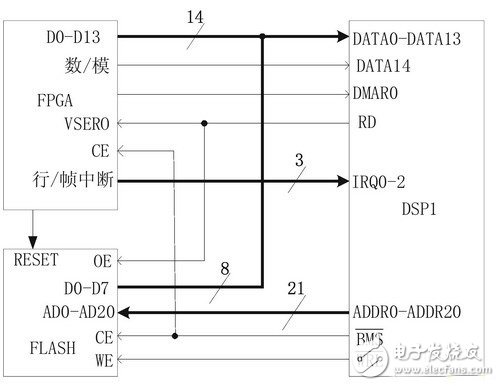

DSP1并行口应接FPGA输出的视频数据,还要接FLASH,完成DSP加载。DSP1的IRQ0,IRQ1分别作视频输入的帧中断和行中断,接到FPGA。其连接电路如下图3所示。

图2DSP1与FPGA,FLASH 连接图

评论