低功率IQ调制器的基带设计实例—电路精选(1)

调制参数

在本设计实例中,系统规格指标如下:

符号率 = 30 ksps

数字滤波器 = 0.35

下一步是确定基带滤波器要求:

总的信号 BW = 30 * 1.35 = 40.5kHz,这对于每个 I 和 Q 通道即为 20.25kHz。这决定了滤波器通带。

滤波器阻带要求在很大程度上由 DAC 更新速率决定,在该场合中为 240ksps,即每个符号 8x 插值。

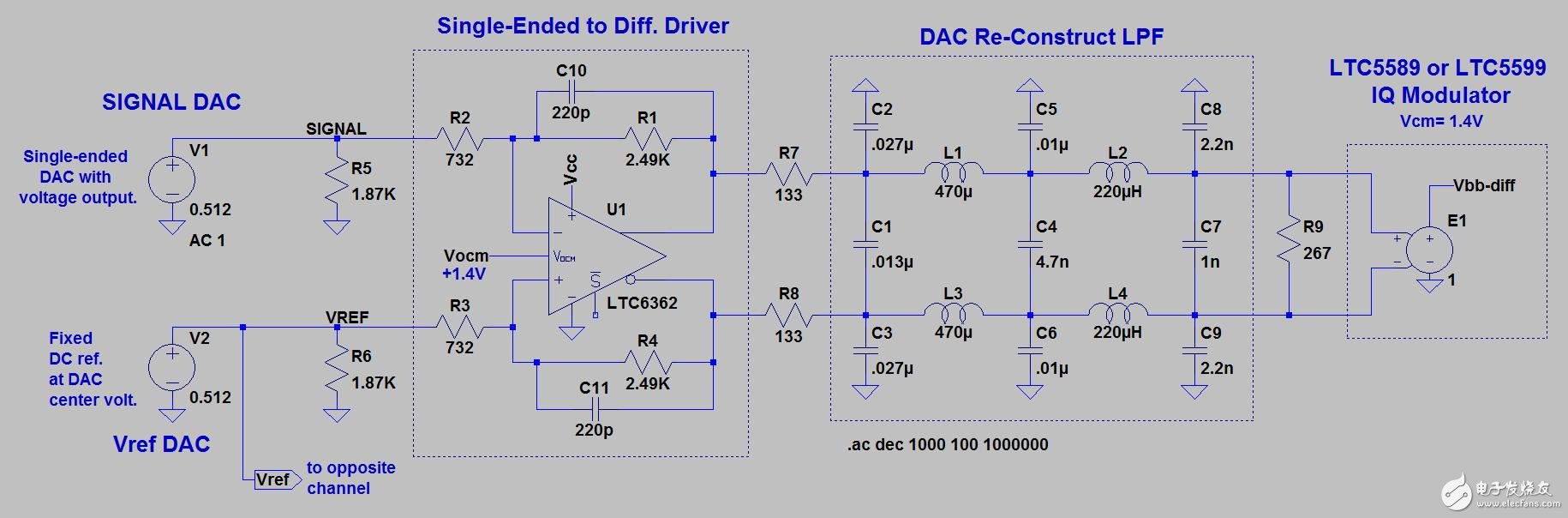

现在让我们快进到完整的电路,然后再做描述。请注意:为简单起见,仅示出了两个相同的通道 (I 和 Q) 之一:

图 1:基带驱动电路把单端 DAC 转换至差分。推荐采用无源 DAC 重构滤波器以实现低噪声。

DAC 输入和基准

差分 DAC 输出是更可取的。但是,当采用单电源、单端 DAC 输出时,则一个固定 Vref 变得必不可少,它可以来自第三个 DAC,或来自信号 DAC 的 VREF。Vref 就是 DAC 的零基准,而且它能在 I 和 Q 通道之间共用,但是应确保其为低源阻抗,以在 I 和 Q 通道之间实现串扰的最小化。如有必要,可利用一个 LTC6246 电压跟随器对 VREF 进行缓冲。

在该例中,单端 I 和 Q DAC 针对 0 至 +1.024V 输出进行配置。请注意,应对 DAC 数字驱动进行调整以使用所有可用的 DAC 位,但是绝对不要触及全标度极端值。

任选的电阻器 R5 和 R6 的选择以实现从 DAC 吸收低平均 DC 电流为目标。在本实例中,输入共模电压被下拉至 0.512V,以与 DAC 输出电压范围的中心相匹配。

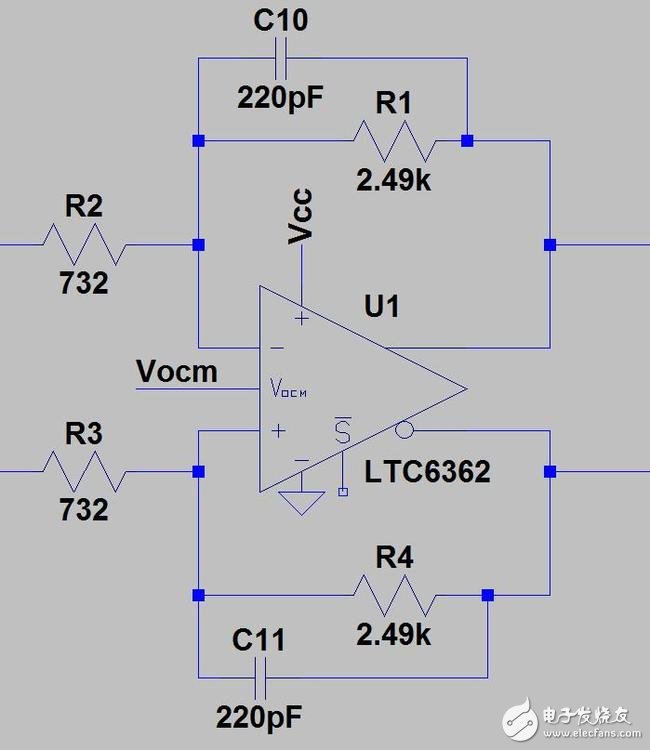

单端至差分驱动器

与单端基带驱动截然不同,采用差分基带信号来驱动调制器是高度可取的。差分驱动可提供高 6dB 的 RF 输出功率和最低的误差矢量幅度 (EVM)。

另外,选择一个具差分输入和输出的放大器还可简化设计,这是因为:

设计对称性减少了输出 DC 失调误差,这降低了 LO 馈通 (LOFT) 并改善了调制准确度。

输出共模电压 (VOCM) 可单独地变更以满足调制器的要求,而且

增益可以单独地变更,并不会影响 VOCM。

图 2:差分驱动器通过提供增益和输出共模电压的单独调整简化了设计。

针对该应用选择了 LTC6362,因为该器件仅吸收 1mA 的电源电流,而且噪声相当低。对于那些基带信号源具有低接近噪声密度 (这意味着一个非常高阶数的基带数字滤波器与高分辨率 DAC 一起使用) 的设计,低的放大器噪声是很重要。我们不望放大器使该接近信噪 (S/N) 比指标出现任何劣化。

电容器 C10 和 C11 的选择旨在削减高频 (HF) 噪声,同时在极高的基带频率下产生可忽略的 (《0.1dB) 幅度误差。LTspice 仿真对于该目的是相当有用的。

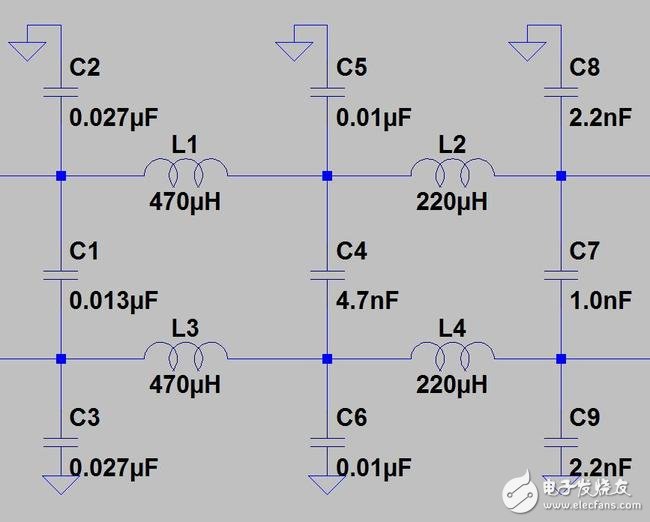

DAC LC 重构滤波器

DAC 重构滤波器对于使 DAC 阶梯状输出平滑是很重要的,它可减少高频奈奎斯特镜像。另一个重要功能是最大限度地降低调制器输出端上的宽带噪声层。

图 3:LC 重构滤波器。该设计针对的是 266Ω 信号源和负载终端。

采用传统的滤波器设计 CAD 工具来合成用于设计的 LC 元件值。为获得最佳的调制准确度,应选择针对线性相位的贝塞尔 (Bessel) LPF 响应。在本例中,-3dB 拐角被置于 50kHz,这适合于高达 ~30ksps 的符号率。

DAC 镜像杂散信号的幅度 (相对于期望信号) 可利用 SIN(x) / x (式中的 x = π f / fCLK) 来估算。对于该设计的频率计划,我们可预期在 220kHz 实现 25dB 的镜频衰减。把 DAC LC 重构滤波器在 220kHz 提供的衰减 (45dB) 加至此衰减,旨在估算 70dB 的总奈奎斯特镜频抑制。

评论