内存条的PCB布线经验

根据我们现在的项目经验,对内存设计经验进行一点整理总结:

1、内存的选型:

首先是满足客户的要求,主要是容量上的要求。

其次,在容量大小一样的情况下,尽量选择速率较低的,这样会降低后续PCB的设计难度,而且由于时钟频率较低,会获得比较好的信号完整性,噪声容限也较大。

再次,在封装上,如果空间足够,优先选择TSOP封装,因为双排引脚式的封装在布线空间上要优于FBGA封装,而且在调试时更方便。

最后,在数据位宽上,如果客户没有特别要求,选择X16位宽的内存,这种内存最为常用,而且相比X32位宽的内存,在PCB布线上要节省很多的布线空间,节省叠层。

2、去耦电容和端接电阻的选择布局:

3、布线方法:

这里主要讲的是双面对贴的内存的布线方式,单颗内存布线方式没有什么要求,连通就可以了。

BGA封装和TSOP封装两种内存的双面对贴布线方式是一样的,下面主要以美光公司的SODIMM 8颗粒DDR内存条举例说明走线方式。

关于走线规则的问题在此不再赘述

这里主要讨论两片内存的网络共用和引脚交换的问题。

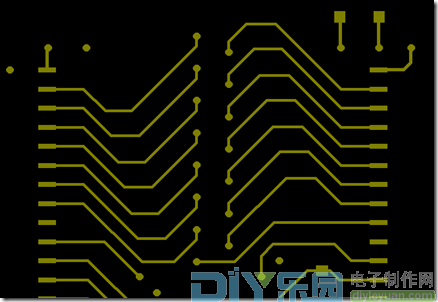

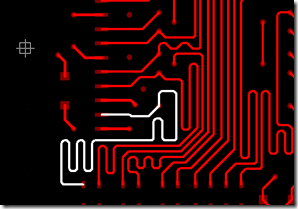

地址线网络直接公用,走线打孔方式采用对排纽扣式,如下图所示:

![13LT8RBX`~SVKU1PTL14~]N](http://editerupload.eepw.com.cn/fetch/20160830/1942_0_0.jpg)

上图是美光公司设计的SODIMM内存条的正面DDR、背面DDR和透视的地址线公用布线图,采用的是双排钮扣式打孔方式,目的是为了保证CPU到各个内存的地址线都是等长的。

对于数据线的分支方式,最好也采用这种双排钮扣式走线方法,但是由于布线空间的限制,在内存两排引脚中间的空间有限,从地址线的走线已经可以看出,两排过孔的上下两端分别外扩,继续这种方式走线已经不可能。因此,对于数据线网络的公用,我们采用数据引脚交换的方式。

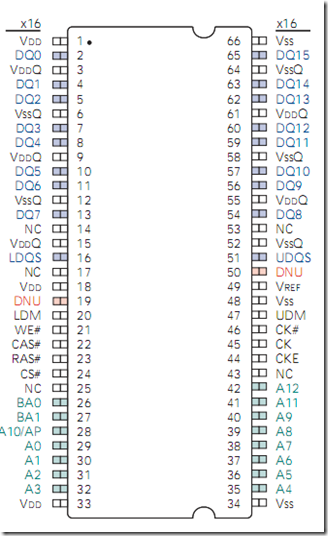

首先我们看一下DDR内存的引脚分布情况:

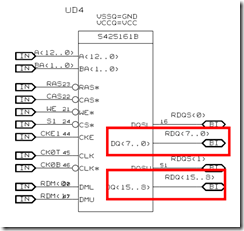

下图是美光公司的512MX16位宽内存的引脚分布图:

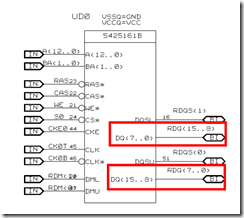

从引脚分布图可以看出,如果两片内存采用对贴的方式,则第一片的DQ0与第二片的DQ15对应,DQ1与DQ14对应,如此等等。即第一片DDR的低八位和第二片DDR的高八位对应。为了节省布线空间,在原理设计时可以让第一片低八位与第二片的高八位共用同一个数据网络,如下所示:

注意:

对于第二片DDR,如果数据引脚已经交换(CPU的DQ0连接DDR的DQ15等),那么相应的数据选通信号和数据屏蔽信号的高低位也需要交换。

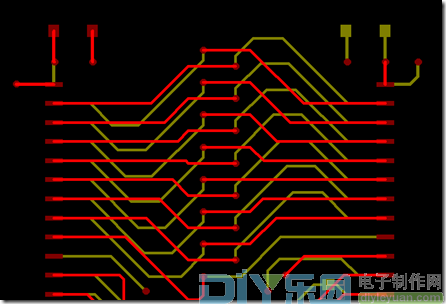

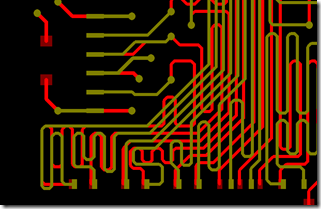

PCB布线图如下所示:

对于其他的信号,如控制、时钟信号等,都是公用同一个网络,因此过孔打在两排引脚的中间,这样公用网络到每片内存的走线长度都相等。

具体的gerber文件和原理图可以从美光公司的官网上免费获得。

3、端接电阻:

现在内存的时钟速率越来越快,基本的DDR内存的时钟频率最低为133MHz,根据传输线理论,在FR-4基材上,信号的走线长度超过800Mils时就需要考虑信号的传输线效应了,因此对于内存的走线来说,基本上所有的信号线都需要加上端接电阻。通常数据信号和控制信号都采用源端串联端接,端接电阻常用22欧姆,采用电阻排的形式。时钟信号采用源端并联端接,端接电阻通常选择100~120欧姆。

技术资讯 技术方案 技术应用 技术新品 技术前沿 行业资讯 行业方案 行业应用 行业新品 行业前沿

评论