欠采样:基于SARADC的应用和技术

以低吞吐量运行SAR ADC可以实现多种优势。通过增加转换操作之间的时间,可以放宽系统滤波器要求,增加获取输入信号及从ADC抽取数据的时间。由于ADC的采集周期是转换周期中读取数据最常用的区域,因此,延长采集周期将放宽数字主机的要求。可以采用主机输出-从机输入(MOSI)时钟速率较慢的低端处理器。例如,AD7980 16位SAR ADC的额定采样速率最高为1 MSPS。

ADC的繁忙周期的最大额定值为710 ns,读取数据的时间只剩下290 ns。要输出16位数据要求时钟周期不超过18 ns(或者不低于55 MHz左右)。然而,如果器件运行时的吞吐量为100 ksps,结果会使采集时间(数据读取周期)从290 ns增至9290 ns。降低ADC采样速率后,可以放宽串行时钟要求,并把最小串行时钟频率改为2 MHz左右。在放宽数字主机要求以外,延长采集时间后,由于增加了建立时间,因此,还可以选择使用低功耗和低带宽ADC驱动器。

只要ADC支持需要的系统连续时间信号带宽,就可以考虑使用额定最大吞吐量较低的ADC(如AD7988-1),以降低系统成本。AD7988-1是与AD7980同系列的一款100 ksps SAR ADC器件,它以较低的价格提供了相同的性能。如图1所示,器件的功耗与采样速率呈线性关系,因为多数功耗发生在活跃转换周期中。减少转换过程的次数,消耗的电量也会减少。速率为100 ksps时,AD7980(或AD7988-1)的功耗约为AD7980以1 MSPS的速率采样时的十分之一。

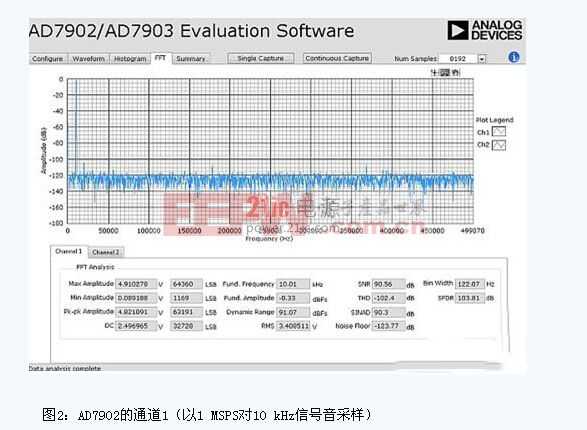

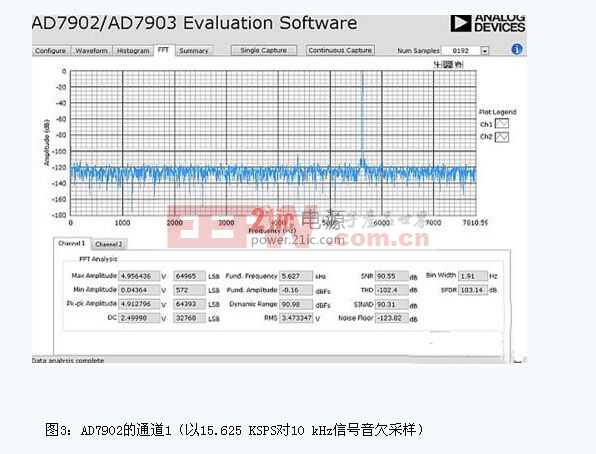

在单通道16位伪差分AD7980以外,ADI系列同时提供AD7902。这是一款双通道16位伪差分同步采样ADC,其额定采样速率为1 MSPS。在传播时间等应用中,可以利用同步采样系统来抽取信号相位信息。我们收集了AD7902以1 MSPS和15.625 ksps(1 MSPS的1/64)的速率对10 kHz信号音采样时的实验室结果。运用等式4,欠采样10 kHz信号音的基频应该出现在DFT频段中,该频段跨度为5.625 kHz。可以看出,在符合奈奎斯特标准的采样与欠采样配置之间,无幅度信息丢失。但重构信号将为原始连续时间输入的第一奈奎斯特区混叠表示。

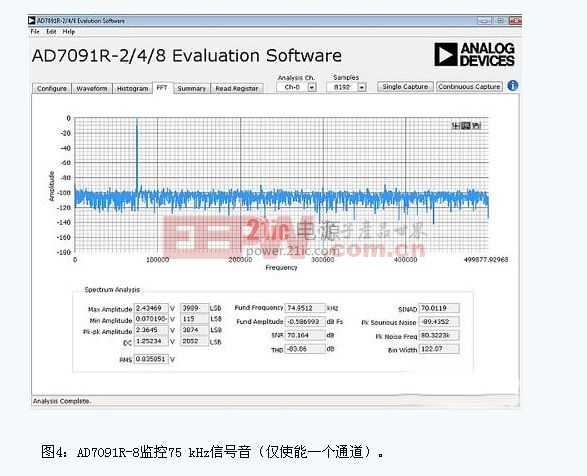

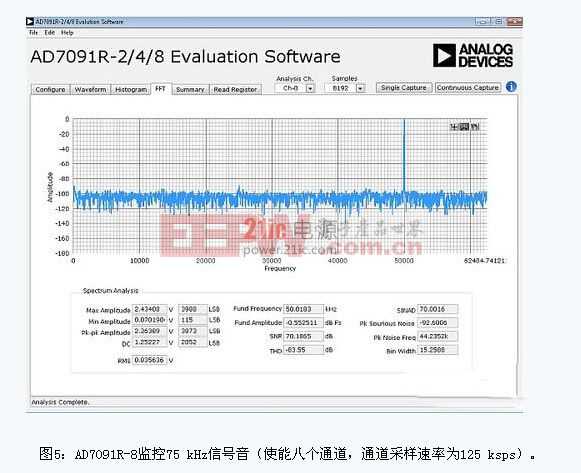

欠采样可能具有优势的另一个例子是多通道顺序采样数据采集系统。这些系统一般由一个SAR ADC构成,带有一个多路复用模拟前端,以固定间隔按已知顺序转换。在这种情况中,各个通道的有效采样速率以系统中使能通道数的函数下降。例如,在一个八通道系统中,如果SAR ADC运行于1 MSPS下,则每隔八个样本代表一个相应的通道。因此,给定通道的采样速率仅为1 MSPS的1/8(125 ksps)。可以看到,在一个多路复用顺序采样系统中,单个通道的奈奎斯特频率是如何快速降低的。

ADI公司提供AD7091R-8,这是一款超低功耗的12位、八通道1 MSPS SAR ADC,内置一个基准电压源和一个用户可编程的通道序列器。该器件采用4 mm x 4 mm LFCSP微型封装,工作于3 V电源和1 MSPS采样速率时,其功耗不高于1.7 mW。在AD7091R-8上,如果使能全部八个通道,器件就会按从通道0到通道7的顺序,自动重复顺序采样。当ADC的采样速率为1 MSPS时,每个通道将以125 ksps的速率采样。因此,相对于1 MSPS单通道系统,给定通道的奈奎斯特频率从500 kHz降低到62.5 kHz。在多路复用器的一个通道上监控75 kHz信号音,结果会产生连续时间信号的混叠表示,其基频为50 kHz。如后续各图所示,当通过使能AD7091R-8上的额外通道修正奈奎斯特标准时,动态性能并未下降。

本文阐述了这样一种想法:在通信系统以外,有些应用可以用到欠采样理论。这些应用可能包括RMS-DC转换、交流应变计、传播时间、超声电平测量和多路复用采样。用SAR ADC实现欠采样系统可能带来巨大的性能和功耗优势。不但可以放宽系统的总体限制,同时还能实现电路的总体目标。

评论

速率为100 ksps

看看