FPGA四大设计要点解析及应用方案集锦

本文叙述概括了FPGA应用设计中的要点,包括,时钟树、FSM、latch、逻辑仿真四个部分。

FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。早期的FPGA相对比较简单,所有的功能单元仅仅由管脚、内部buffer、LE、RAM构建而成,LE由LUT(查找表)和D触发器构成,RAM也往往容量非常小。现在的FPGA不仅包含以前的LE,RAM也更大更快更灵活,管教IOB也更加的复杂,支持的IO类型也更多,而且内部还集成了一些特殊功能单元,包括:

DSP:实际上就是乘加器,FPGA内部可以集成多个乘加器,而一般的DSP芯片往往每个core只有一个。换言之,FPGA可以更容易实现多个DSP core功能。在某些需要大量乘加计算的场合,往往多个乘加器并行工作的速度可以远远超过一个高速乘加器。

SERDES:高速串行接口。将来PCI-E、XAUI、HT、S-ATA等高速串行接口会越来越多。有了SERDES模块,FPGA可以很容易将这些高速串行接口集成进来,无需再购买专门的接口芯片。

CPU core:分为2种,软core和硬core。软core是用逻辑代码写的CPU模块,可以在任何资源足够的FPGA中实现,使用非常灵活。而且在大容量的FPGA中还可以集成多个软core,实现多核并行处理。硬core是在特定的FPGA内部做好的CPU core,优点是速度快、性能好,缺点是不够灵活。

不过,FPGA还是有缺点。对于某些高主频的应用,FPGA就无能为力了。现在虽然理论上FPGA可以支持的500MHz,但在实际设计中,往往200MHz以上工作频率就很难实现了。

FPGA设计要点之一:时钟树

对于FPGA来说,要尽可能避免异步设计,尽可能采用同步设计。同步设计的第一个关键,也是关键中的关键,就是时钟树。一个糟糕的时钟树,对FPGA设计来说,是一场无法弥补的灾难,是一个没有打好地基的大楼,崩溃是必然的。

具体一些的设计细则:

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心;

3)跨时钟域的信号一定要做同步处理。对于控制信号,可以采用双采样;对于数据信号,可以采用异步fifo。需要注意的是,异步fifo不是万能的,一个异步fifo也只能解决一定范围内的频差问题。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处。

5)对于特殊的IO接口,需要仔细计算Tsu、Tco、Th,并利用PLL、DLL、DDIO、管脚可设置的delay等多种工具来实现。简单对管脚进行Tsu、Tco、Th的约束往往是不行的。

可能说的不是很确切。这里的时钟树实际上泛指时钟方案,主要是时钟域和PLL等的规划,一般情况下不牵扯到走线时延的详细计算(一般都走全局时钟网络和局部时钟网络,时延固定),和ASIC中的时钟树不一样。对于ASIC,就必须对时钟网络的设计、布线、时延计算进行仔细的分析计算才行。

FPGA设计要点之二:FSM

FSM:有限状态机。这个可以说时逻辑设计的基础。几乎稍微大一点的逻辑设计,几乎都能看得到FSM。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。实际使用中大部分都采用merly型。

FSM通常有2种写法:单进程、双进程。

初学者往往喜欢单进程写法,格式如下:

always @( posedge clk or posedge rst )

begin

if ( rst == 1‘b1 )

FSM_status <= 。。.。。.;

else

case ( FSM_status )

。。.。。.;

endcase

end

简单的说,单进程FSM就是把所有的同步、异步处理都放入一个always中。

FPGA设计要点之三:latch

首先回答一下:

1)stateCAD没有用过,不过我感觉用这个东东在构建大的系统的时候似乎不是很方便。也许用system C或者system Verilog更好一些。

2)同步、异步的叫法是我所在公司的习惯叫法,不太对,不过已经习惯了,呵呵。

这次讲一下latch。latch的危害已经说过了,这里不再多说,关键讲一下如何避免。

1)在组合逻辑进程中,if语句一定要有else!并且所有的信号都要在if的所有分支中被赋值。

always @( * ) begin

if ( sig_a == 1‘b1 ) sig_b = sig_c;

end

这个是绝对会产生latch的。

正确的应该是

always @( * ) begin

if ( sig_a == 1’b1 ) sig_b = sig_c;

else sig_b = sig_d;

end

另外需要注意,下面也会产生latch。也就是说在组合逻辑进程中不能出现自己赋值给自己或者间接出现自己赋值给自己的情况。

always @( * ) begin

if ( rst == 1‘b1 ) counter = 32’h00000000;

else counter = counter + 1;

end

但如果是时序逻辑进程,则不存在该问题。

2)case语句的default一定不能少!

原因和if语句相同,这里不再多说了。

需要提醒的是,在时序逻辑进程中,default语句也一定要加上,这是一个很好的习惯。

3)组合逻辑进程敏感变量不能少也不能多。

这个问题倒不是太大,verilog2001语法中可以直接用 * 搞定了。顺便提一句,latch有弊就一定有利。在FPGA的LE中,总存在一个latch和一个D触发器,在支持DDR的IOE(IOB)中也存在着一个latch来实现DDIO。不过在我们平时的设计中,对latch还是要尽可能的敬而远之。

FPGA设计要点之四:逻辑仿真

仿真是FPGA设计中必不可少的一步。没有仿真,就没有一切。仿真是一个单调而繁琐的工作,很容易让人产生放弃或者偷工减料的念头。这时一定要挺住!仿真分为单元仿真、集成仿真、系统仿真。

单元仿真:针对每一个最小基本模块的仿真。单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%!这三种覆盖率都可以通过MODELSIM来查看,不过需要在编译该模块时要在Compile option中设置好。

集成仿真:将多个大模块合在一起进行仿真。覆盖率要求尽量高。

系统仿真:将整个硬件系统合在一起进行仿真。此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。系统仿真是逻辑设计的一个大分支,是一门需要专门学习的学科。

Xilinx针对平板显示器LED背光的FPGA解决方案

1.概述

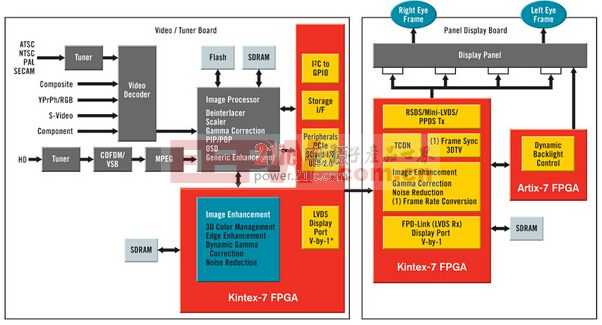

Kintex-7 FPGA 和 Artix-7 提供的功能使得平板显示器制造商能够提高图像质量、降低功耗和削减成本。

2.方案特性

为 LED 背光控制器实现了复杂的局部调光和照明补偿算法。

生产具有不同的 LED 区域数量和 LED 布局的直接型照明显示器,同时调整照明以便与不同供应商生产的面板的物理特性相匹配。

为显示器添加 3D 功能。

与利用上一代 FPGA 实现的设计相比,其系统 FPGA 功耗降低了32%

与利用上一代 FPGA 实现的设计相比,其系统 FPGA 成本削减了30%

利用 Artix-7 FPGA 实现的设计将 LED 背光控制器的功耗降低 63%

灵活的并行/串行接口技术利用 PCI Express、USB 2.0、DisplayPort 和 V-by-One 技术实现了芯片-芯片和板-板通信

3.75Gbps V-by-One@HS 的 16 或 32 信道 (per Thine’s spec)

5.4Gbps DisplayPort 1.2 的多端口 (per VESA spec)

1,866Mbps DDR3 存储器接口实现了基于商用存储器的视频数据缓冲器

1.6Gbps LVDS I/O 降低了并行接口内的迹线数量

芯片级封装实现了基于4层 PCB 的低成本生产

方案框图:

3.业界领先的系统解决方案

KintexR-7 FPGA 能够提供高信号处理能力和低功耗,从而满足各种应用需求,包括:

1)LED 背光平板显示器和 3DTV

2)LTE 基带

3)携帯型超音波装置

4)多模射频

5)高端消费类数码单反相机

6)Video-over-IP 网关

相关芯片介绍:赛灵思Kintex-7 FPGA 系列芯片简介

基于京微雅格低功耗FPGA的8b/10b SERDES的接口设计

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

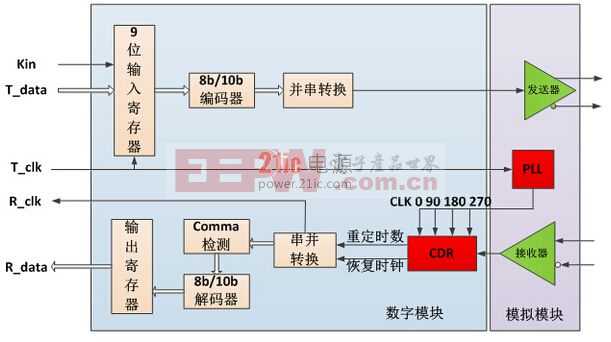

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现 8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等 特点。

1硬件接口:

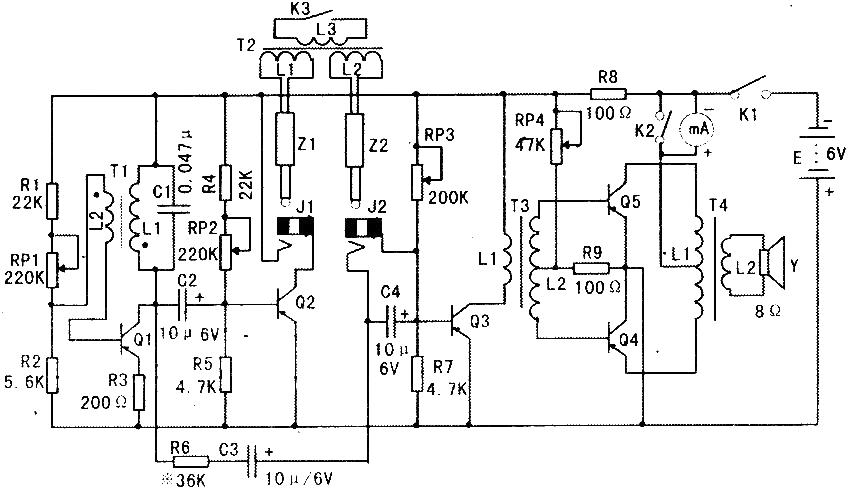

硬件的接口如上图所示,主要包括发送与接收模块。

发送模块包括8b/10b编码器,并串转换器,锁相环(PLL)频率合成器和发送器,接收模块包括 8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的 10 位8b/10b 编码,并串转换用于将 10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将 CMOS 电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

在接收端,接收器将接收到的低摆幅差分信号还 原为 CMOS 电平的串行信号,CDR 从串行信号中抽取时钟信息,完成对串行数据的最佳采样,串并转换利用 CDR 恢复的时钟,将串行信号转换成 10 位的并行数据,Comma 检测器检测特殊的 Comma 字符,调整字边界,字边界正确的并行数据经过 8b/10b 解码,还原为字节信号,传送到上层协议芯片,完成整个信息传输过程。

实际的设计中,CDR部分是由纯逻辑电路完成的,为设计的核心的部分,下面将介绍数字CDR在HR03的实现方案。

2数字CDR:

CDR模块作用是从数据中恢复嵌入的时钟,然后接收器按照恢复的时钟进行数据位对齐并通过comma进行字对齐。最后,将数据进行8b/10b解码,供系统使用。

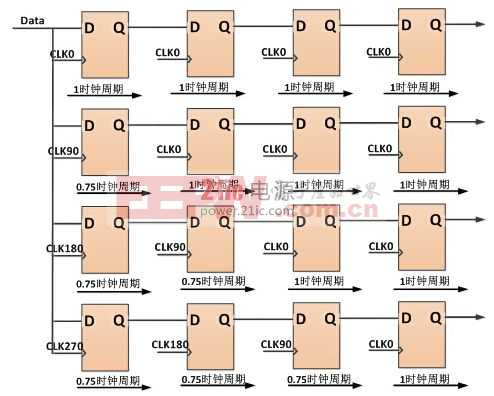

本方案采用同频多相的时钟采样方法,具体实现过程利用PLL产生4个时钟频率相同,相位相差90度的时钟,分别为clk0、clk90、clk180、 clk270,这四个时钟输出完全同步,利用4个时钟对数据进行采样,以获得4倍过采样的效果,具体的实现过程如下图所示:

在数据时钟恢复时,将到来的数据分别输入到四个触发器,分别用4个不同的相位进行采样,要注意保证从输入引脚到四个触发器的延迟基本一致。

第一列触发器的触发分别由时钟CLK0、CLK90、CLK180、CLK270的上升沿触发,按照这样的方式来触发就可以得到四个数据采样点。这样就 将原始时钟周期分成了四个单独的90度的区域,如果系统时钟为200MHz,上图所示的电路就相当于产生了800MHz 的采样速率。

仅通过一阶的触发器,输出的采样数据存在亚稳态的问题,因此需对采样点作进一步的处理。这里可将四个采样点通过进一步的触发,除掉亚稳态的问题,从而使采 样点移到下一个相同的时钟域。通常,亚稳态的去除要经过两三级的处理,这就使得在有效数据输出前会有数位无效的数据,在数据采样的第一个阶段,电路检测数 据线上数据的传输。当检测到有数据传输时,对传输数据的有效性进行确认。确认数据有效后,输出高电平来指示采样点有数据传输。

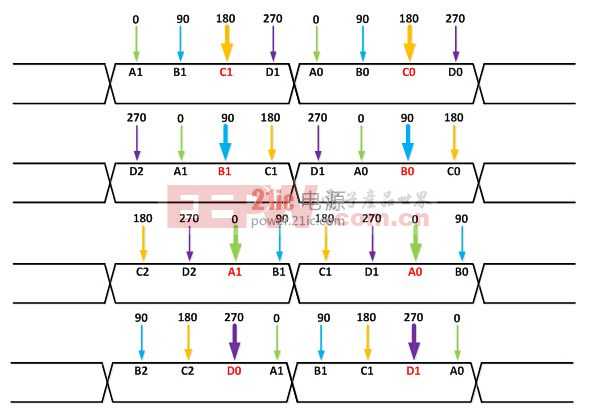

因为最终有四个输出,所以需要一个复用器来选择数据。发送数据与采样时钟的对应关系如上图所示,其对应关系分为4种情况,每种情况下对应一个最佳的采样 时钟,系统通过对数据边沿位置信息的判断,来确定哪路时钟为最佳采样时钟,并利用复用器从选定的时钟域中选择数据位,例如检测电路确定从时钟域A中采样的 数据有效,那么将时钟域A中采样的数据通过输出端输出。

3结束语:

通过对纯数字电路的CDR电路,在没有硬核的支持下,完成了FPGA上SERDES的接口设计,并通过实验的传输测试,在HR03的FPGA上,可完成100~200Mbps的数据传输。

基于FPGA的智能小车设计方案

智能监控机器人是近年来机器人应用工程中一项前沿性的题目,智能化探测小车是智能行走机器人的一种。智能监控机器小车就是针对上述情况,在参考 了目前大多数智能机器人的基础上,以降低成本为原则设计的。小车具备温湿度和环境监测、无线通信、躲避障碍物以及无线遥控等功能。此智能监控机器小车与目 前已有的同类设计相比,有性价比高、操作方便、可靠性好、功耗小等优点。

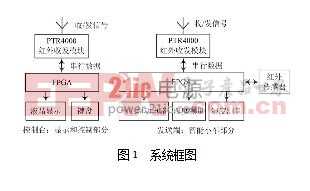

1 系统结构及硬件设计

整个系统由发送端(智能小车部分)和接收端(控制台:控制和显示部分)组成,如图1所示。系统由传感器系统、动力及转向系统、CCD图像传感器模块、 LCD显示、温度和湿度测量电路和供电系统等组成,整个系统的控制核心以2片Altera公司的EP2C20F484为核心,在Altera公司的 QuartusⅡ和SoPC Builder开发环境中完成。根据系统硬件结构添加所需要的外围模块并生成NiosⅡCPU。

1.1 供电系统

小车安装了两块充电电池,分别为FPGA开发板(FPGA控制电路)和小车运动提供能量,电池置于车身底部。

1.2 传感器系统

系统采用了6个红外对射传感器,通过FPGA配置的NiosⅡCPU来检测传感器信号实现小车躲避障碍物的功能。漫反射型红外对射传感器也称光电开关, 是一种集发射器和接收器于一体的传感器,多用于检测障碍物。原理是由光电开关辐射出来的调制红外光束被检测物体反射回来,红外线经同步选通接收,由电子开 关线路驱动回路,从而来检测物体的有或无。当被检测物体的表面光亮或其反光率极高时,漫反射式的光电开关是首选的检测模式。这种电路模块体积小,信号容易 转化为标准电平。

1.3 动力及转向系统

本小车有左右轮两个电机及龟机驱动。驱 动电路采用了CT Microelecttonics公司的大功率直流电机驱动芯片L298,最高支持50 V电压,最大电流为5 A,满足大功率电动机的要求,外围电路简单,同时,由于该芯片为双路结构,分别控制左右电动机,增加了电路的可靠性,减少了复杂性。电机控制采用PWM脉 冲宽度调制方式来控制汽车的前进速度。由NiosⅡCPU写入控制字,可得到不同占空比的PWM驱动信号,此PWM信号送入电机驱动芯片的控制端来调节速 度。

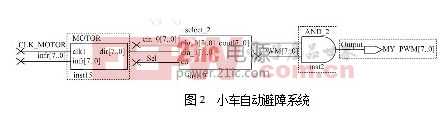

1.4 小车自动避障系统

小车自动避障系统采用Verilog HDL语言编写驱动电路。该模块(见图2中的MOTOR)和一个数据选择器(见图2中的select_2)相连来实现自动避障与人工遥控之间的切换。当小 车上NiosⅡCPU的SEL管脚输出低电平时,数据选择器将把该模块的输出作为电机的控制指令。这样设计的好处在于设计具有响应迅速,不需要NiosⅡ CPU参与,提高了CPU处理湿度、温度数据并控制无线模块收发数据的效率。该逻辑电路的工作原理是根据红外传感器发回来的数据,经过逻辑判断来控制电机 的工作状态。

1.5 小车的人工控制

小车的人工控制和自动避障之间的转换由一个数据选择器控制,当小车上NiosⅡCPU的SEL管脚输出高电平时,数据选择器将把无线模块所发送过来的指令作为电机的控制指令,实现了对小车的无线控制。

1.6 温度和湿度测量

在温度测量系统中,采用抗干扰能力强的新型数字温度传感器DS18B20,该系统设计中将DS18B20的1,3引脚分别接于FPGA板的GND 和+3.3 V管脚,2引脚接FPGA的I/O脚,传输控制及数据信号。DS18B20最高可用12位表示温度值,最高5位为符号位。

采用HS1101湿度传感器,具有响应速度快,工作温区宽(-40~+100℃),测量范围大(0%~100%RH),可靠性高,稳定性好,功耗低,外围电路简单等优点。

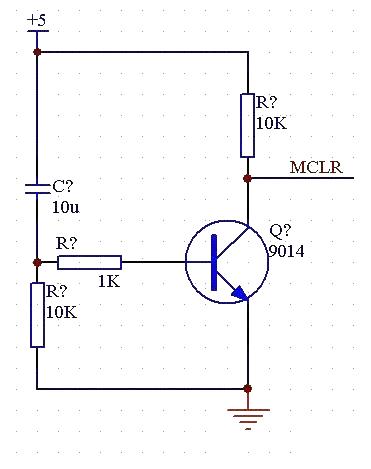

工作原理为:用HS1101传感器与TLC555构成多谐振荡器,HS1101传感器内部电容会随湿度的变化而变化,从而使输出频率发生变化。编写VHDL程序在FPGA设计一个频率计可精确的测出频率值,通过输出频率与湿度的关系便可得到湿度值。

1.7 无线收发系统

系统采用PTR4000无线嵌入式模块,工作频率为2.4 GHz,最高工作速率可达1 Mb/s,高效GMSK调制,且有CRC检错功能。具有低功耗,抗干扰能力强,体积小等优点。主要有三种工作模式,分别为:配置模式、 ShockBurst发送模式和ShockBurst接收模式。

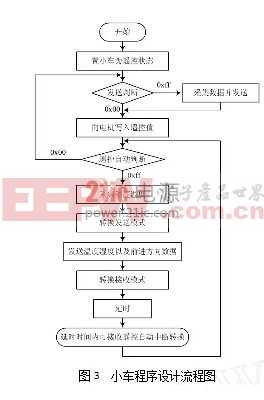

2 软件设计和调试

采用NiosⅡ进行C语言编程。NiosⅡ集成开发环境(IDE)是NlosⅡ系列嵌入式处理器的基本软件开发工具。所有软件开发任务都可以在Nios ⅡIDE下完成,包括编辑、编译和调试程序。NiosⅡIDE是基于开放式的、可扩展Eclipse IDE project工程以及EclipseC/C++开发工具(CDT)工程,NiosⅡIDE为GCC编译器提供了一个图形化用户界面,可以支持标准C。 NiosⅡIDE编译环境自动地生成一个基于用户特定系统配置(SoPC Builder生成的SoPC文件)的makefile,有利于程序的开发。

NiosⅡIDE包含一个强大的、在GNU调试器基础之上的软件调试器——GDB。完成软件代码的编写后,可以对代码进行仿真和调试。Nios-Ⅱ IDE提供了一个方便的闪存编程方法。任何连接到FPGA的兼容通用闪存接口(CFI)的闪存器件都可以通过NiosⅡIDE闪存编程器来烧结。针对本设 计及应用,编写了系统控制程序和LCD显示程序。流程图如图3所示。

3 系统调试

小车系统需要测试能否准确接收控制台发送的指令并控制小车运动或停止,以及向前、后、左、右转向。还要测试主控机能否准确接收小车采集到的温度以及湿度 信息,能否正确显示。经过多次测试,发现由于系统程序是采用收发循环转换的模式,为了让两个系统能够收到对方发的信息,对小车的遥控与自动部分进行简单的 分化。自动情况下,控制台为主要接收端,小车为主要发送端,一般情况下小车发送数据到控制台,需要自动到遥控的转换时,通过在延时时间内进行中断来实行从 自动到遥控的转换;在遥控状态下,控制台为主要发射端,小车为接收端,一般情况下控制台发送小车行进指令到小车,需要采集数据时,通过温度、湿度采集按键 来对小车进行收发转换,同时小车发出采集数据指令,之后再次转为接收模式。这样做之后使小车与控制台的软件部分清晰明了,小车的行进以及采集显示数据能够 实时的进行。

湿度测量系统需要测试是否能够精准输出频率值。采用芯片LM555手册上推荐的电路,由于元件的误差,使输出的频率并不精 确,经过与标准的湿度仪进行比对,通过参数调整,用直线做近似,最后得到的频率值误差在几赫兹(频率范围是6 008~7 314Hz),经过预算得到很准确的湿度值。开始求湿度值时用的是解一元三次方程的方法,由于计算量大,对小车的行进会有很大影响,后来在小车端只是把小 车采集到的频率值通过红外天线传输到主控端,并将原先的小车自动避障由NiosⅡCPU控制改为由Verilog编写的硬件模块控制,最后在控制台做湿度 值的计算。这样的更改既减少了小车NiosⅡCPU的工作量,同时由于小车的自动避障改为由独立的Verilog模块控制,运行起来很流畅。

对于无线收发系统,要测试其可靠性以及发送或接收的信息的准确性。测试方法是单独设计了一个软核下载到SoPC中,并编写一段程序用于测试是否正确写入 配置控制字,是否能够进行ShockBurst模式的接收或发送。问题是对天线各模式时序的把握,一开始写的程序总是不能正确写入配置字,反复调试,并用 数字示波器观察写入配置字的瞬间过程以及各延时的时间,最后测试成功,并把发送或接收的状态用LED显示出来,每发送或接收到一个数据包就让LED闪一 下。

4 结语

本设计以FPGA嵌入NiosⅡ软核处理器为核心,辅以必要的外围 电路,构成了高度集成化的片上系统。另外,SoPC系统的柔性配置,使得可以基于此系统扩展片外存储器和多路输出。设计的小车具有较强的避障能力,且能通 过接收端对其进行方便的控制,温度和湿度采集均达了较高的精度,并且能实现动态显示,无线收发模块的有效范围最远可达300 m,可应用于较为恶劣的环境,可代替人进行温度和湿度的实地检测。

评论