双向飞碟射击与设计调试

纵观历史,电路内仿真 (ICE) 模式是使用硬件仿真器的第一种方式,也是迄今为止最为流行的方法。在这种模式中,需将硬件仿真器插入物理目标系统上的插孔,以此代替待开发的芯片,从而利用实时数据支持运用和调试硬件仿真器内部映射的待测设计(DUT)。

然而,这种公认的能够引人注目的验证方法却存在一系列问题,其中最严重的问题便是它的随机性。也就是说,当调试DUT时,它缺少确定性或者可重复性。为了更好地理解这一点,我们可以做个形象类比。

让我们来看看双向飞碟射击。这是一种射击运动,在这项运动中,会将碟靶从靶场上扔出以模拟鸟类的飞行状态。我们可以增加碟靶的扭转方向,增加它的难度。让射手戴副眼镜,以限制他的视野范围,这样射手必须“猜测”碟靶的轨迹,因为碟靶的每一次轨迹都不一样。而验证工程师在 ICE 模式中调试芯片设计时,恰恰也会遇到这样的难题。要在 ICE 模式中找出一个错误就像在狭窄的视野中试图击中碟靶一样困难。

图 1 要在视野受限的情况下进行双向飞碟射击对射手来说是一项巨大的挑战。

我们不断总结过去的经验,持续改进。这二十多年来,不断有调查发现设计验证消耗的时间大约占了设计周期的 70% 左右。往好的方面看,设计验证是一项活动,它或多或少地可以根据预测事先进行安排。但是设计调试则是一项追击,您无法事先对其进行规划。理由很简单,错误往往会因为未知的原因出其不意地出现,而且您也无法预测它出现的时间和位置。

可以想象,在利用大量嵌入式软件和硬件进行片上系统 (SoC) 设计时,总有些错误会隐藏在设计的某个未知角落里,无论是在硬件中还是在软件中,而且这些错误可能只有在长期执行后方能被发现。在一个错误被发现之前,很有可能已历经了数十亿的时钟周期。

更让人沮丧的是,调试具有随机性,这就要求在发现错误之前要不断地重复运行。如果错误不具备确定性,也就是说,其可能不会在后续运行中重复出现,那么寻找错误的过程将会是一场噩梦。

关键未知因素

如果将其应用于数亿门级的设计,而这些设计需要经过数十亿个长序列验证周期的调试,那么可能存在三个关键未知因素:地点、时间和事由。这三个因素足以延误整个测试计划的进度,即便该计划已经过深思熟虑。在一个竞争激烈的市场中,若一项新产品延期三个月上市,那么它将造成 33% 的潜在总收益损失。这就足以说明验证解决方案的价值所在了。这时我想到了硬件加速仿真。硬件仿真器凭借其极速性能加快执行和调试的速度。事实上,它们的快速执行速度便是它们的设计初衷。

这个概念很简单,即对照需要插入待开发芯片的实际物理目标系统来检查 DUT。无需再编写测试矢量或者测试激励。赶紧在实际应用中全面施行这一流程吧。想必,要在模糊的设计区域里寻找令人厌烦的隐匿错误,实际应用比任何软件测试平台都更为有效,对吧?

在线调试问题

结果证明,闪闪发光的并非都是金子。尽管它的功能非常诱人,但要在 ICE 模式中调试芯片设计会显得过于繁琐而又令人沮丧,究其原因,主要有两点。第一点,硬件仿真器必须要与目标系统相连。就此而言,由于硬件仿真器的速度可能比物理目标系统慢上三个数量级,因此就需要有一个速度适配器,可以调解物理目标系统较快的时钟速度,使之与硬件仿真器的相对较慢的速度相匹配。基本上,该适配器是一个先进先出 (FIFO) 的寄存器,它通常会通过牺牲部分功能和准确性来换取性能。同时,PCIe 或以太网等高速协议也将会减少,以应对 FIFO 内在能力的局限性。

适配器和连接电缆增加了设置的物理关联性和弱点,同时也对系统的可靠性产生了不利影响。此外,设置仅局限于每个协议一个测试实例,且不允许存在特殊用例测试或任何“假设”分析。最后,如果没有人在现场提供帮助,将仿真器插入和拔出目标系统,则无法远程访问ICE 模式。

第二点,也是最容易被人低估的一个缺点,便是它缺少确定性行为。这一特性会使目标系统用以验证设计的方法变得折中,还会延长在ICE模式下发现错误的时间。在 ICE 模式中,使用硬件仿真器追踪 DUT 的错误,需要在特定事件被触发后,以最高速捕捉设计中每个寄存器的行为。在基于定制硅的硬件仿真器中,无需编译连接程序,就可将每个设计寄存器连接到追踪存储器中。在运行时间方面,验证工程师可进行权衡折衷,即使用追踪时钟周期的数量来交换需要追踪的设计寄存器的数量。

在商用的、基于FPGA的硬件仿真器中,只有少量的设计寄存器可以通过编译程序连接到追踪存储器上。增设或者更换追踪寄存器就要求重新编译设计,同时大幅减少设计/迭代时间。利用这两种硬件仿真器,用户可以通过减少被追踪的寄存器的数量来增加追踪深度,反之则亦然。

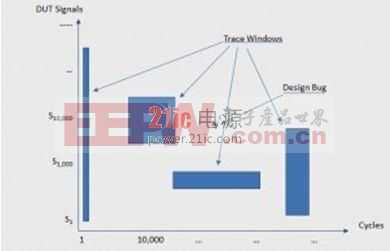

图 2 追踪窗口(周期 X 信号)受逻辑分析仪中内存容量的限制。

因此,用户可以不再为了找到自己感兴趣的调试窗口和转储正确的波形而进行多轮——很可能是数百次的运行。但是真正的问题是,每次运行都可能会在不同的时间点发现错误——相同的错误;甚至更糟糕的是,还可能因为不可预测的行为而发现不了任何错误。还记得双向飞碟射击的例子吗?

来看下使用第三方 IP 填充 SoC 的例子。屡次测试表明,当 IP 核单独工作时,其能起到作用;但当它内嵌于 SoC 时,却变得完全无效。利用 ICE 模式对深埋于 DUT 的 IP 进行调试可能会导致验证团队没日没夜地加班。

图 3 连续运行时,会在不同的时间/区域内显示相同的设计错误或者根本不显示任何设计错误。

值得高兴的是,随着基于事务处理的协同建模技术的出现,硬件仿真领域也发生了翻天覆地的变化。通过移除物理目标系统,并使用虚拟测试环境进行代替,所有问题都消失不见了。这种虚拟测试环境是通过 C++/SystemVerilog 从高抽象层次进行描述,并通过事务处理器与 DUT 相连。

测试平台可用性

可以在很短的时间内通过 SystemVerilog 创建高层次测试平台,这样不仅符合传统的 Verilog 的要求而且错误也较少。事务处理器都有现货可买,无需定制。还有,整个测试环境将目标锁定在多媒体、网络和存储等特定的市场应用程序上,涵盖了虚拟测试程序和事务处理器,而这些都可在 Mentor Graphics 旗下支持其 Veloce2 硬件仿真平台的 VirtuaLAB 品牌中找到。

更重要的是,如今的设计激励是具确定性的,因此可以更快完成调试。事务处理器可以实现从HDL软件仿真到硬件仿真的平稳过渡。时钟可以停止,也可以进行单步调试;可以进行情境“假设”分析;还可以对特殊用例进行建模。如今,工程师可以通过编写寄存器传输级 (RTL) 代码来设计芯片,而不需要利用实验室设备来测试他们的设计。目前,远程访问已经实现了而且会越来越普及。

将 SystemVerilog 断言与事务处理器结合,验证工程师们可以利用无限的调试功能监控他们的设计,并且不会降低速度。如此,工程师们就可以尽情设计,不再会受到内存空间或者时间的限制,然后尽快消除错误。自此以后,工程师与视野受到限制的双向飞碟射击比赛的选手将无任何共通之处。

评论