FRAM芯片扩展耐力在低功耗应用

动翻译,供参考

FRAM芯片扩展耐力在低功耗应用

虽然EEPROM和闪存通常都被用于非易失性存储器(NVM)的最佳选择,在大多数应用中,铁电RAM(FRAM)提供了许多低功耗设计在能量收集应用,例如无线传感器节点,智能电表明显的优势,和其他数据记录的设计。凭借其扩展的写周期耐力和数据保留时间,FRAM技术可帮助设计人员满足使用的FRAM芯片和基于FRAM微控制器的制造商,包括Cypress半导体,富士通半导体制造商ROHM Semiconductor要求十年之久,低功耗的NVM操作和德州仪器。

常规NVMS,诸如闪存和EEPROM,在在浮动栅,需要一个电荷泵,以提高电压以需要通过栅极氧化物来强制载波的水平电荷载体的形式存储数据。其结果,沿着与长写延迟和高功率消耗固有这些设备中,它们的高电压写入操作最终可以穿出细胞 - 有时在少至万个写周期。

FRAM优势

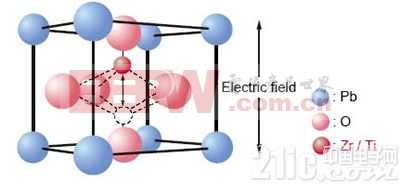

与此相反,铁电RAM(FRAM)存储由铁电材料锆钛酸铅的偏振的装置,或PZT(Pb(上ZrTi)O 3),它被置于两个电极类似的电容器的结构之间的膜。与DRAM中,在FRAM中阵列的每一位被读出和单独写入,但在DRAM的使用的晶体管和电容器来存储比特,FRAM采用在晶体结构中的偶极移引起的施加电场的相应位跨电极(图1)。因为该偏振仍然是去掉电场之后,FRAM数据仍然存在无限期即使没有可用功率 - 用于设计搭载不确定环境来源的重要能力。

富士通半导体FRAM细胞电场的图像

图1:在FRAM细胞,数据存储为偏振引起的施加电场横跨PZT膜的状态 - 一种方法,使扩展的数据保留,并消除在浮栅技术中遇到的磨损。 (富士通半导体提供)

随着使FRAM的非挥发性,利用晶体的偏振提供了许多优于基于电荷的存储技术的优点(见表1)。因为它避免了浮栅技术的潜在的降解效果,FRAM存储器和其保存数据的功率损耗的面能力的寿命几乎是无限的。例如,FRAM存储器设备,如富士通半导体MB85R1001A和ROHM半导体MR48V256A所有指定10年的数据保持性能。

FRAM

EEPROM

FLASH

SRAM

Memory Type

Non-volatile

Non-volatile

Non-volatile

Volatile

Write Method

Overwrite

Erase + Write

Erase + Write

Overwrite

Write Cycle Time

150 ns

5 ms

10 μs

55 ns

Read/Write Cycles

1013

106

105

Unlimited

Booster Circuit

No

Yes

Yes

No

Data Backup Battery

No

No

No

Yes

表1:FRAM与其它存储器技术比较。 (富士通半导体提供)

通过省去了在浮栅存储器技术所需电荷泵,FRAM可以在3.3V或更低的典型电源范围内工作。此外,与存储电荷的存储器设备,FRAM装置具有耐α粒子和通常表现出软错误率(SER)检测极限以下。

设计的影响

的FRAM的优势的影响涟漪通过的系统,例如无线传感器节点,需要高速写入和低功耗工作的组合的设计。例如,对于它的高速率,设计者可以使用一个单一的FRAM装置,其中,他们可能需要并联布置以达到可接受的数据写吞吐率多个EEPROM器件。在这些设计中的EEPROM,而一个EEPROM器件正在完成其写周期时,控制器将启动一个写操作的下一个EEPROM器件上的顺序,等等。使用FRAM,但是,所有的写操作发生在一个随机存取的基础总线速度,没有基于内存的延迟或其他写放缓。其结果是,FRAM存储器典型地实现在相当低的能量需求显著更快的写入比闪存。

设计人员还可以不再需要必须确保数据的完整性电源的备份策略。用一个EEPROM系统中,存储器控制器必须完成一个完整的写周期被检测到电源故障时所需要的数据块大小 - 需要额外的能量储存,以确保在基于EEPROM的设计写周期完成。凭借其快速的循环时间,FRAM能够即使在突然停电,完成写作过程中,从而保证了数据的完整性,无需复杂的电源备份方法。

在应用层面,FRAM的快速写入速度和低功耗操作也能连续测量能量采集应用,如无线传感器或电能表。在给定的功率预算,FRAM设备将能够完成更多的读/写循环的一个更精细的粒度比可能与其他NVM技术。

FRAM还介绍了开发人员提供一个统一内存架构,使代码和数据灵活的分区,并允许一个更简单的,更小的单芯片的内存解决方案。同时,设计人员可以很容易地防止使用简单的写保护电路,以提供基于FRAM的设计(图2,HC151多路复用器)可编程块写保护功能意外写入存储在FRAM的代码。

赛普拉斯半导体HC151低功耗的多路图像

评论