智能晶振电路建议及设计方案

在我们设计单片机电路中都会用上晶振,它结合单片机内部的电路,产生单片机所必须的时钟频率,单片机的一切指令的执行都是建立在这个基础上的,晶振提供的时钟频率越高,那么单片机的运行速度也就越快。因此,一个高效的晶振电路对于单片机系统稳定性具有至关重要作用。为此,本文将基于对晶振性能的深入研究,结合本人的实践经验为广大同行提供一个晶振电路设计方案。

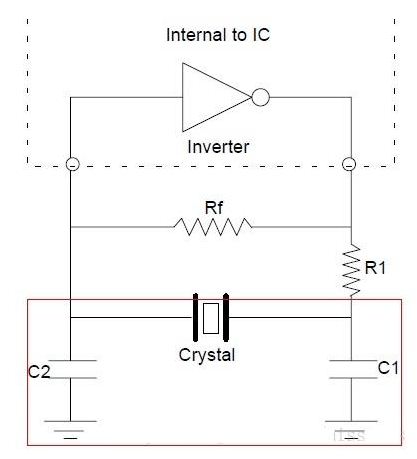

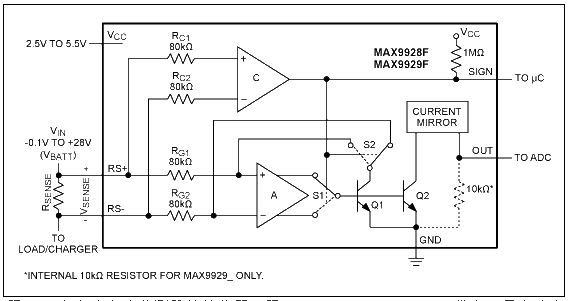

如下图为晶振振荡电路图。这样的组成可以使晶振处于并联谐振模式。反相器在芯片内体现为一个AB型放大器,它将输入的电量相移大约180°后输出;并且由晶振,R1,C1和C2组成的π型网络产生另外180°的相移。所以整个环路的相移为360°。这满足了保持振荡的一个条件。其它的条件,比如正确起振和保持振荡,则要求闭环增益应≥1。

图1.晶振振荡器设计电路

反相器附近的电阻Rf产生负反馈,它将反相器设定在中间补偿区附近,使反相器工作在高增益线性区域。电阻值很高,范围通常在500KΩ ~2MΩ内。图示的C1,C2就是为晶振工作在并联谐振状态下得到加载电容CL的电容。关于最优的加载电容CL的计算公式为:

这里CS是PCB的漂移电容(stray capacitance),用于计算目的时,典型值为5pf。现在C1和C2选择出来满足上面等式。通常选择的C1和C2是大致相等的。C1和/或C2的数值较大,这提高了频率的稳定性,但减小了环路增益,可能引发起振问题。这样对设计和调试带来很大的麻烦。不同的环境温度下对C1/C2取值有差异,带来电路一致性不好等系列问题。

R1是驱动限流电阻,主要功能是限制反相器输出,这样晶振不会被过驱动(over driven)。R1、C1组构成分压电路,这些元器件的数值是以这样的方式进行计算的:反相器的输出接近rail-to-rail值,输入到晶振的信号 是rail-to-rail的60%,通常实际是令R1的电阻值和的C1容抗值相等,即R1 ≈ XC1。这使晶振只取得反相器输出信号的一半。要一直保证晶振消耗的功率在厂商说明书规定范围内。过驱动会损坏晶振。

理想情况下,反相器提供180°相移。但是,反相器的内在延迟会产生额外相移,而这个额外相移与内在延迟成比例。为保证环路全相移为n360°,π型网络应根据反相器的延迟情况,提供小于180°的相移。R1的调整可以满足这一点。使用固定大小的C1和C2,闭环增益和相位可随R1变化。如果上述两个条件均得到了满足,在一些应用中,R1可以忽略掉。实际使用达不到自适应的效果。

一些芯片如EPSON的SPXO晶振SG-210STF内置了C1、 C2,因此减少了产品在样品和量产时的频偏调试时间,消除了电路设计师的烦恼。这种情况下,只要把晶振连接在XTAL和XTAL引脚上,添加电阻即可。

提示:

1)在PCB板上缩短线路可以减小漂移电容。这也有利于解决晶振起振和振荡频率的问题。

2)为了取得最好效果,晶振的设计,用至少0.4 Vdd(峰峰值)的电平驱动时钟反相器。

评论