基于AES的网络加解密系统系统硬件图及完整源代码

1、作品简介

本作品以AES-128/192/256算法的相似性为基础,设计一个AES加/解密IP核,在32位的Microblaze软核下,并配合相应的软件完成网络传输数据的加密与解密功能,实现可根据具体应用资源数与安全系数需求而灵活配置以达到最佳性能的动态可配置加/解密系统。AES从设备作为系统的协处理器专门负责完成数据的加解密操作,通过总线从存储器中取出数据,然后将计算结果返回给存储器,网络控制器负责网络数据与缓冲区数据的传输,再利用32位Microblaze处理器和FPGA完成外围电路,使之和处理器集中在一块芯片上减小了系统的体积,简化了系统的规模,在一定意义上实现了片上系统。具有硬件结构简单、运行速度快、安全性高、实用价值高等优势,可被广泛应用于网路信息安全领域。

本作品中的AES加/解密IP核提供3种长度的密钥可以根据资源多少以及安全系数需求的具体情况灵活选择。并针对总线接口规范,设计了相应接口及其地址空间的映射,使该IP核能够方便的作为系统自定义组件使用。通过32位Microblaze处理器的调度,该系统可以处理任意长度的数据,可灵活的应用于各种数据加密。同时该设计以精简硬件结构为目标,与传统的以吞吐率为目标的流水线模式AES加/解密系统相比,具有消耗硬件资源小,性价比突出的优点。并利用FPGA的片上存储模块加快读写速度,在S盒的设计上采用可重构技术,使整个设计具有了更高的安全性、可靠性与灵活性。

2、作品的总体设计方案

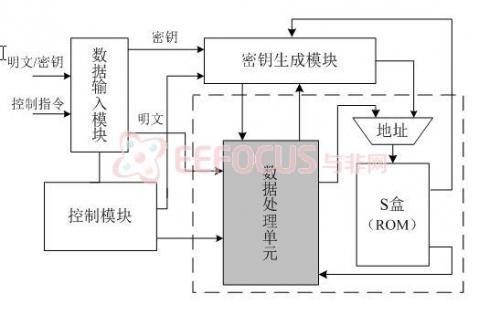

本作品包括硬件设计部分与软件设计部分,硬件设计主要是自定义AES IP核,并完成硬件系统板级的设计和连接工作,优化处理性能及各模块效率,完成数据传输的接口电路、完善外围电路及辅助外设。软件设计部分主要是AES组件的驱动程序,组件调用常用函数以及应用程序的编写,主要是对计算机接口的数据进行校验和加/解密验证显示。图2.1和2.2分别给出了硬件设计框图和软件设计框图。

图2.1系统硬件结构图

图2.2系统软件流程图

2.1 硬件设计

2.1.1 AES组件的设计

该AES IP核包含两条路径,加密路径和解密路径。由于AES算法不是完全的对称,所以加、解密路径是由各自的硬件构成。其加/解密流程如图2.3所示。

图2.3 AES 加/解密流程

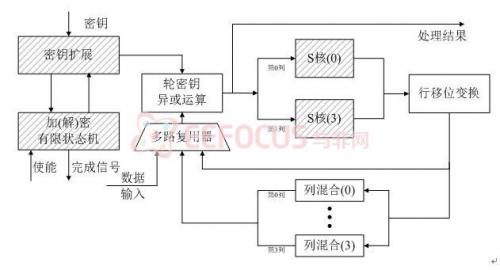

以AES算法的数据块为研究对象,来设计整个IP核的各个子模块。首先,需要确定该IP核的接口,考虑到该IP核的可移植性,本文采用PLB总线接口规范,控制总线中包含时钟信号、复位信号、控制使能信号、功能选择信号、状态信号和中断信号。其次,根据数据块的加解密流程可将该IP核划分为:有限状态机模块(Fine State Machine)、密钥扩展模块(KeyExpansion)、轮密钥异或运算模块(AddKey)、字节替换模块(SubByte)、行移位变换模块(ShiftRow)、列混合模块(MixCol)和多路复用器模块(AddKeyMux)七部分,如图2.4所示;有限状态机模块与多路复用器模块共同控制着IP core 的整个迭代过程,使得数据块在其它各个模块正确的运行完成加/解密操作。

图2.4 IP核结构图

为了方便该IP core作为自定义组件用于系统集成,该IP core设计了内存映射空间。在系统中,总线宽度为32位,IP core所有的写操作都是基于从端口的写传输,一个时钟周期传输32位数据,加/解密的数据块需要多个时钟周期来完成输入。因此,该IP core设计的关键在于接口设计及其地址空间映射、有限状态机的设计和密钥扩展模块的设计。

IP核设计中主要介绍以下几个重要模块的设计,比较简单的模块不再赘述。

(1)S 盒变换模块

S盒变换是该算法硬件实现时的重要环节,在整个算法中占用了比较大的资源,本设计中,采用近年来对AES S盒硬件实现的改进策略,将查找表的内容存储到FPGA内部的存储器中,根据输入字节的数值进行快速的查表操作,避免了传统设计使用CASE语句描述而占用大量的逻辑资源。同时该设计让加/解密共用一个S盒模块,将S盒和逆S盒设计成一个可重构处理单元,然后在处理单元内部增加了一个可控节点,使它即能用于加密又能用于解密。

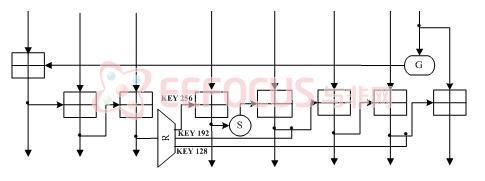

(2) 可配置密钥扩展模块

分析AES 3种密钥长度的密钥扩展算法可知,128、192Bit的密钥生成圈函数都可视为256Bit密钥生成圈函数的一部分[4],因此可以将3种密钥扩展算法设计为一个可配置的共用模块。本设计以256Bit密钥生成算法圈函数为基础,在其内部添加了1个控制单元R,通过控制指令选择路径,即可改变内部结构及和其它模块的连接关系,从而灵活匹配不同类型的密钥算法。密钥扩展算法的可配置结构设计如图2.5所示。

图2.5 AES密钥扩展算法的可配置结构

(3) 接口设计及其地址空间映射

该IP core所有信号都是同步的,时钟上升沿有效,具体接口信号设计如表2.1所示。

表2.1 IP core 接口信号

|

信号名称 |

信号位宽 |

信号方向 |

信号描述 |

|

clk |

1 |

in |

总线时钟 |

|

reset |

1 |

in |

同步复位信号 |

|

writedata |

32 |

in |

根据地址从数据总线上写入32位数据 |

|

address |

5 |

in |

地址信号,5位地址即可表示32个地址空间 |

|

write |

1 |

in |

写使能信号 |

|

read |

1 |

in |

读使能信号 |

|

readdata |

32 |

out |

根据地址从数据总线上读出32位数据 |

|

waitrequest |

1 |

out |

等待信号 |

|

irq |

1 |

out |

中断信号 |

根据表2.1可以看出所有的接口信号都是按照总线规范设计的,这样使本设计能够直接作为自定义组件集成到系统中使用。IP core的密钥、加/解密数据以及所有的控制信号都是通过32位数据总线传输的,为了使IP core能够识别,需设计出合理的地址空间映射,如表2.2所示。

表2.2:IP core地址空间映射

|

地址偏移量 |

名称 |

描述 |

|

0X00-0X07 |

KEY |

初始密钥,为只写内存区 |

|

0X08-0X0B |

DATA |

输入处理数据,为只写内存区 |

|

0X10-0X13 |

RESULT |

处理结果数据,为只读内存区 |

|

0X14-0X1E |

|

保留 |

|

0X1F |

CTRL |

控制状态字 |

表2.2中,控制寄存器CTRL控制着IP core的功能和轮询的状态,它是可读可写模式。本设计只用到4个字节的第0个字节,第1到第3个字节保留待用。控制寄存器CTRL各位的映射如表2.3所示。

表2.3 控制寄存器映射

|

偏移位 |

名称 |

描述 |

|

31-8 |

|

保留 |

|

7 |

KEYVALID |

密钥有效位 |

|

6 |

IRQENA |

中断使能端 |

|

5-2 |

|

保留 |

|

1 |

DEC |

解密模式 |

|

0 |

ENC |

加密模式 |

(2) 有限状态机控制模块

该IP core加/解密工作首先需要初始化一个密钥,密钥初始化完毕后就会启动密钥扩展模块,产生各个轮运算所需要的轮密钥,轮密钥产生完成后,传入需要操作的数据块,然后根据有限状态机的控制完成各轮加/解密,最后完成操作,加/解密有限状态机如图2.6所示。

图 2.6 加/解密有限状态机

3.2 软件设计部分

嵌入式系统的软件,用于协调各个子模块和数据的调用,是实现设计者思想的主要手段。软件模块主要包括AES组件相关程序与应用程序。

部分主要代码如下:

// AES头文件

#ifndef AES_H_

#define AES_H_

#define KEYWORDS 8

#define AES_BASEADDR 0x02902000

#define KEY_ADDR AES_BASEADDR+0x00

#define DATA_ADDR AES_BASEADDR+0x08

#define RESULT_ADDR AES_BASEADDR+0x10

#define AESCTRLWD AES_BASEADDR+0x1F

typedef struct{

volatile unsigned int* key;

volatile unsigned int* payload;

volatile unsigned int* result;

volatile unsigned int* control;

} aes_handle;

void aes_init(aes_handle* context);

void aes_setKey(aes_handle* context, unsigned int* key);

void aes_setPayload(aes_handle* context, unsigned int* payload);

void aes_setKeyvalid(aes_handle* context);

void aes_encrypt(aes_handle* context);

void aes_decrypt(aes_handle* context);

int aes_isBusy(aes_handle* context);

#endif /* AES_H_*/

// AES常用函数

#include < aes.h>

#include <string.h>

void aes_init(avs_aes_handle* context){

context->key = (unsigned int*) KEY_ADDR;

context->payload= (unsigned int*) DATA_ADDR;

context->result = (unsigned int*) RESULT_ADDR;

context->control = (unsigned int*) AESCTRLWD;

*(context->control) = 0x00000000;

}

void aes_setKey(avs_aes_handle* context, unsigned int* key){

int i=0;

unsigned int* target_ptr = (unsigned int* )context->key;

// Invalidate old key;

*(context->control) &= (~0x00000080);

for(i=0; i<KEYWORDS; i++){

*(target_ptr++) = *(key++);

}

// validate key;

*(context->control) |= 0x00000080;

}

void aes_setPayload(aes_handle* context, unsigned int* payload){

int i=0;

unsigned int* target_ptr = (unsigned int* )context->payload;

for(i=0; i<4; i++){

*(target_ptr++) = *(payload++);

}

}

void aes_setKeyvalid(aes_handle* context){

*(context->control) |= 0x00000080;

}

void aes_encrypt(aes_handle* context){

*(context->control) |= 0x00000001;

}

void aes_decrypt(aes_handle* context){

*(context->control) |= 0x00000002;

}

int aes_isBusy(aes_handle* context){

unsigned int mycontrol = *(context->control);

return mycontrol & 0x03;

}

3、作品仿真测试

本作品以Xilinx的XC6LX16-CS324为目标芯片,在Quartus II 8.0平台上进行了综合、布局、布线,利用ModelSim进行仿真测试。

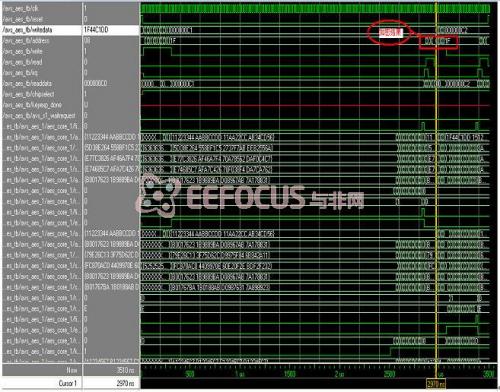

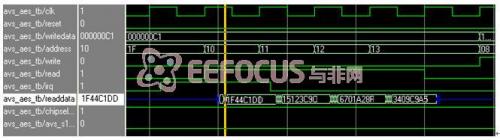

AES加/解密组件仿真测试:仿真时钟为100MHz的情况下,其仿真波形分别如图3.1、图3.2所示。

图3.1 AES加/解密组件功能仿真结果

图 2.3 AES加/解密组件时序仿真结果

其中,输入的密钥为:

A1234567_B1234567_C1234567_D1234567_E1234567_F1234567_A7654321_B7654321(长度为256Bit),

测试数据为:

11223344_AABBCCDD_11AA22CC_AB34CD56(长度为128Bit),

AES加/解密结果为:

1F44C1DD_15123C9C_6701A28F_3409C9A5。

仿真结果与软件运行的加/解密结果一致,该IP核在功能与时序上都达到了预期的目的。

系统测试:

根据编写好应用软件后,完成硬件设计并将其下载到Spartan6开发板上,用户可通过键盘和键盘接口逻辑,输入密钥、测试数据和操作指令,然后通过软件界面窗口的输出获得对测试数据的处理结果,实现了简易的人机交互功能。通过测试程序,可以看到系统能够正确运行。

4、作品的创新和优势分析

创新点:

(1)利用时分复用的AES-128/192/256 IP核,实现网络加/解密的动态可配置。

(2)对设计增加输入安全机制,采用了在内核上对密钥及原始数据进行输入锁定的技术。一旦输入,用户不能再从总线上读取,从而避免从内存窃取信息的可能,增加了系统的安全级别。

优势分析:

(1)可以选择3种不同长度的密钥(128,192,256)对数据进行加/解密,根据具体应用资源数与安全系数需求灵活的配置以达到最佳性能;

(2)可以对一组或几组离散数据进行加密或解密,也可以对一个连续的数据堆进行加密或解密;

(3)在S盒的设计上采用可重构技术,并使整个设计具有了更高的安全性、可靠性与灵活性。

(4)针对组件编写了相关驱动函数,使该网络适配器能够更灵活应用于各种加/解密场所,具有良好的通用性。

6、总结

本作品介绍了一种基于AES算法的动态可配置加/解密网络适配器,采用自动机控制技术辅以软件控制的工作方式,充分利用了FPGA的灵活性和高可配置性,以及硬件加/解密的高效实时性, 较好地兼顾了资源和速度两方面的性能。

Microblaze是Xilinx公司利用各种IP模块集成的软核。它是可编程的,具有灵活的设计方式。在SOPC系统的设计过程中,可根据用户的需要添加Microblaze处理器等相应的IP Core 来完成所需的功能,也可快速裁剪不需要的模块,开发周期短。

本系统以Spartan6实验板为硬件平台,加入了Microblaze处理器、大容量片外内存和网络控制器等IP Core,从而组建起一个完整的SOPC系统。在Microblaze 处理器支持下,可以高效的对该加/解密系统进行控制,充分发挥该系统应对不同资源,不同要求,可灵活配置的特性,并扩展了本系统对网络实时数据进行处理的应用。

由于时间的关系,系统功能还不够完善,在应用程序上还需更合理的安排缓冲区的读写,更好的发挥系统可高效并行处理相同密钥连续数据的速度优势,以应对网络环境下高速数据流的加/解密需求。

评论