一、项目概述

1.1 引言

示波器自1933年诞生至今已经有70多年的历史。它是电子电路设计人员用来观察波形的主要工具,它可以让设计人员直观的看到所要观测到的波形。因此,示波器在信号观测领域一直都扮演着非常重要的角色。传统的模拟示波器信号带宽频率受到阴极射线管的限制而不可能太高,难以测量慢速信号或单次瞬变信号,预触发功能难以实现和不便对波形数据进行数字处理分析等等,因而在许多应用领域中存在着局限性。随着科学技术的飞速发展,单次信号的捕捉,测量和研究越来越受到人们的关注和重视,在信息领域、高速计算机、高速数据通信和高速数字集成电路及其系统内,面临着硬件、软件、以及由软硬件共同作用而产生的偶发性故障,迫切需要更高速的示波器才能得心应手的解决这些难题。随着数字集成电路和高性能微处理器技术的发展,数字存储示波器(DSO)出现了。数字存储示波器整个系统的调节全部由微处理器在相应的软件支持下自动进行,包括自动设置、自动测量、自动校正、波形存储、计算机I/O和打印输出等一系列优点。数字存储示波器的出现开创了示波器的新纪元,它为示波器的智能化打下了坚实的基础,同时它还标志着示波器的发展进入了一个新的时代。

与此同时,波形发生器也是电子工程人员不可或缺的一种工具,常被称作信号发生器,在教学实验或实际工作中作为信号源为电路提供所需的激励信号,因而是一种必不可少的工具。现代新型信号发生器的研制都采用直接数字频率合成(DDS)技术进行,这种技术是第三代频率合成技术的标志,主要特点是计算机参与频率合成,既可以用软件来实现,也可以用硬件来实现,或者二者结合。

本设计研制的多用手持示波表基于美国赛普拉斯公司生产的混合信号可编程芯片PSoC平台。该芯片内不仅集成了51微控制器,还集成了各种数字模块和模拟模块,各个模块可以通过系统内部总线相互通信,所以只用一颗芯片和少许的外围电路就能够完成整个系统的研制。

1.2 项目背景/选题动机

现在市面上的大多数示波器都是台式的,体形过于庞大和笨重,难以携带,对于狭小的场合应用很不方便,在高空作业和其他特殊场合的应用受到很大的限制,加上价格昂贵,动辄几千上万甚至数万元的价格不是每个人都能接受的,另外市面上手持示波表较少,并且功能单一,价格高昂,大部分采样率等较低,实际应用价值不大。

本项目就是基于这种背景下开展的,采用美国赛普拉斯公司生产的混合信号可编程芯片PSoC平台来进行开发,可以有效的减少外围电路,使得示波器可以轻巧玲珑,另外增加了低频率的信号发生器功能,使得该示波器不仅具有示波器功能,还集成了信号发生器的功能。

二、需求分析

2.1 功能要求

(1) 设计一个可以准确显示波形并且能够观察波形参数的示波器,采集电压范围为-20V——20V,分辨率为100mV,可以准确分析信号的频率,电压,功率等参数。

(3)使用PSOC的DAC模块、PGA模块和LPF2模块来实现正弦,三角波,方波输出。

(4)带有锂电池充放电管理,便携的,手持的多功能示波表。

2.2 性能要求

(1)用外置A/D(实时采样率最高为60Mbps)完成对信号的采集,争取能够达到模拟带宽10M以上,实时采样率达到40M以上,实现仪器内触发方式,要求上升沿触发,触发电平可调,并且垂直灵敏度能达到1V, 100mV两档,扫描速度含20ms/div、2μs/div、100ns/div三档,波形周期测量误差≤5%,且被测信号的显示波形应无明显失真,带有FFT,余辉显示等功能。

(2)水平时基可以达到以下范围:2S,1S,500Ms,200Ms,100Ms,50Ms,20Ms,10Ms,5Ms,2Ms,1Ms,500uS,200uS,100uS,50uS,20uS,10uS,5uS,2uS,1uS,500nS,水平位置可调并有指示,存储深度达到5K。

(3)该信号发生器能够产生波形频率范围为0.1Hz~100kHz,频率分辨率为0.1%,输出的电压幅度为0V~5V的波形。

三、方案设计

3.1 系统功能实现原理(除图片外需有文字介绍)

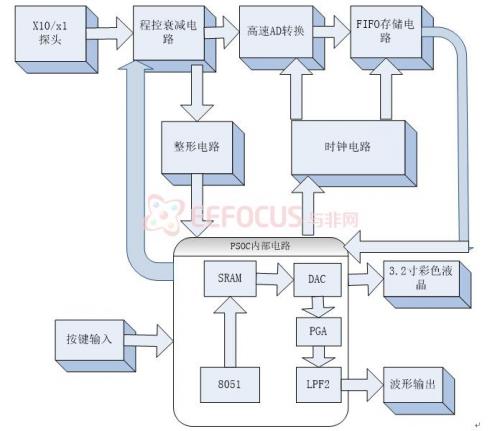

系统硬件结构框图

下面就各个模块电路做以简单介绍

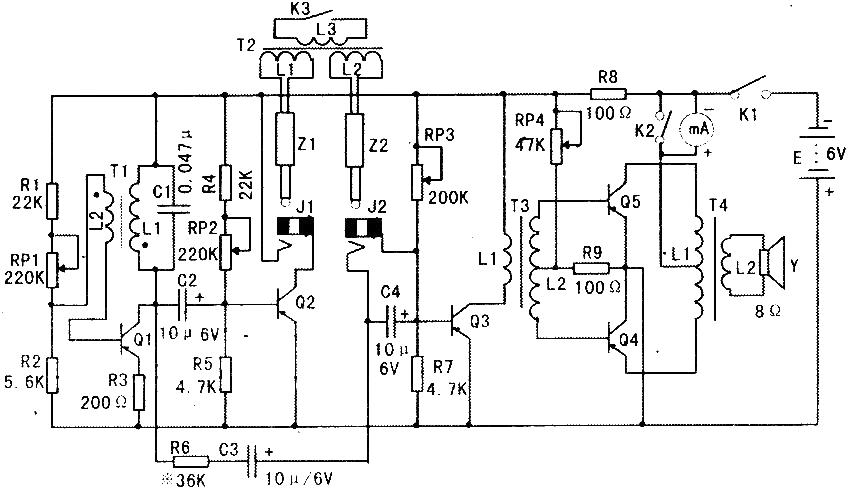

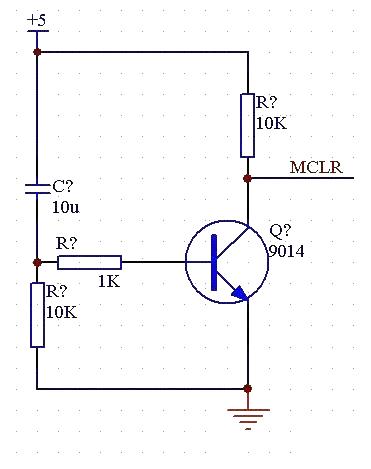

1.程控放大电路和电源电路:

将程控放大电路与电源电路放在一块讲,是因为他们有着密切的联系。

程控放大器的作用是对输入信号进行衰减或放大调整,使输出信号电压在AD转换器输入电压要求范围内,达到最好的测量与观察效果,所以程控放大器电路在规定带宽内的增益一定要平坦,故对运算放大器的要求比较高,在本电路中我选用的是NSC公司生产的高速运算放大器LM6172双运放,带宽为100MHz,转换速率3000v/μs,每通道消耗电流2.3mA,输出电流可达50mA,完全满足本电路的要求,选择该芯片的另一个原因是价格,邮购价格为8元一片,相比ADI,MAX等公司几十元一片的高速运放芯片来说算是很廉价了,电源采用正负双电源供电,由于整个电路总的电源输入为单8v,所以专门用一片dc/dc电路MC34063为其构成了负压转换器再经稳压得到-5v电压,+5v通过对输入电压稳压得到。

2. 高速AD转换与FIFO存储电路

数字示波器中最重要的电路是AD转换电路,它的作用是将被测信号采样并转换成数字信号存入存储器,说它是数字示波器的咽喉一点也不为过,因为它直接决定着数字示波器所能测量的最高频率,根据乃奎斯特定理,采样频率至少是被测信号最高频率的2倍才能复现出被测信号。而在数字示波器中采样频率至少应该是被测信号频率的5~8倍才行,否则根本观察不到信号的波形。在本电路中我选用的AD转换芯片为BB公司的8位高速AD转换器ADS830E,官方资料给出的采样频率为10kSa/s~60MSa/s, 通过实验发现转换速率在1K以下工作也很正常,所以本示波器的最低采样频率为600Sa/s,要说明的一点是高速AD转换器一般都有高低端转换速率的限制,比如TLC5540,8位AD转换器,转换速率为5MSa/s~40MSa/s,我试过当转换频率降到2M以下时就不能正常工作,所以选择AD转换芯片时不仅要注意最高转换速率还要关注最低转换速率,否则可能导致电路无法正常工作。有朋友也许会问8位转换精度会不会有点太低?其实8位转换器对于示波器来说是够用的,就拿这个电路来说,我选用的LCD显示模块的分辨率为320*240,垂直分辨率为240格,而8为转换精度的分辨率为256格,比显示器的分辨率还高,所以绝对够用。还有就是价格及电路的设计,在最高采样率相同的情况下10位AD转换芯片的价格是8位AD转换芯片的几倍,而且位数的增加也使电路的复杂程度大大增加,将直接影响处理速度,导致屏幕刷新过慢,反而影响性能。所以本着够用的原则本示波器选用60M的8位AD转换芯片ADS830E。

3. 时钟产生电路

时钟产生电路为AD转换器提供一系列的采样时钟信号,分别为600Hz、6kHz、60kHz、600kHz、3MHz、6MHz、30MHz和60MHz,共8种,分别对应着不同的水平水平扫速。

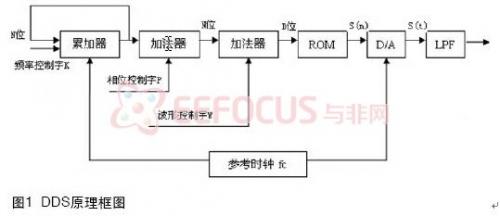

4.信号发生原理DDS介绍

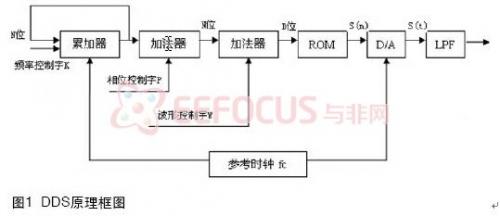

DDS是从相位概念出发直接合成所需波形的一种频率合成技术。一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器(LPF)构成。

DDS的原理框图如图1所示。其中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P、波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位幅度码S(n)经D/A转换器变成阶梯波形S(t),再经LPF平滑后就可以得到合成的信号波形。合成的信号波形的形状取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。DDS系统中除了D/A转换和低通滤波电路外都是数字电路,以往的设计都基于纯数字芯片设计,很难实现单芯片的解决方案,而PSoC的出现刚好满足了这种单芯片、全集成的要求。

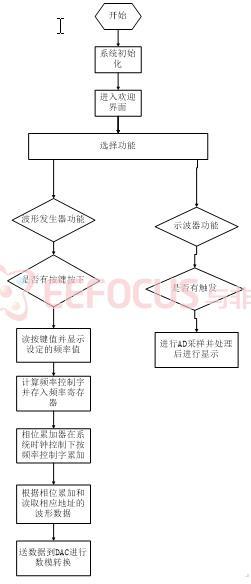

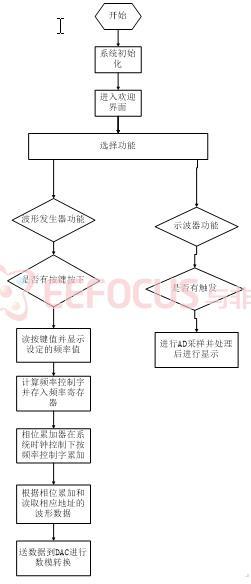

3.2 系统软件流程

程序运行流程图

3.3 系统预计实现结果

制作一个实时采样率可以达到40M以上,模拟带宽可以达到10M以上,带有一定存储深度,显示波形不失真,能够显示任意波形和产生频率范围为0.1Hz~100kHz,频率分辨率为0.1%,输出的电压幅度为0V~5V的三角波,正弦波,方波信号的手持的,便携的示波表。

评论