MCU与USB设备控制器IP核的设计

1引言

在传统的计算机系统上常采用串口(如RS232)和并口连接外围设备,但串口和并口都存在着通信速度慢,接口独占不利于扩展等无法克服的缺点,而通用串行总线(Universal Serial Bus,即USB)因具有传输速度快、支持热插拔、扩展方便、抗干扰强、成本低、数据传输质量高、节省系统资源等优点而得到了广泛的应用,当前它已成为计算机最常用的接口之一。

现在USB控制器主要有两种:带USB接口的单片机(MCU)和纯粹的USB接口芯片。纯粹的USB接口芯片仅处理USB通信,必须有个外部微处理器来进行协议处理和数据交换。典型产品有Philips公司的PDIUSBD11(I2C接口)、PDIUSBD12(并行接口);NS公司的USBN9603/9*(并行接口)。带USB接口的单片机从应用上又可以分成两类,一类是从底层设计专用于USB控制的单片机;另一类是增加了USB接口的普通单片机,如Cypress公司的EZ—USB(基于8051),选择这类USB控制器的最大好处在于开发者对系统结构和指令集非常熟悉,开发工具简单,但价格比较高,不利于产品升级和改型。

然而,国内产品中所用到的USB芯片都依赖进口,主要由国外的IC设计芯片厂商如Cypress,NEC等一些国际著名公司提供。鉴于USB芯片有很好的市场前景和利润空间,尽管国内企业或研究机构目前还只是处于USB芯片应用开发的技术水平,人们还是希望自主开发出有自主知识产权的USB芯片。因此,近年来国内也有许多单位在探索独立设计USB芯片。

本论文针对USB1.1协议规范,本着自主开发USB控制芯片,把MCU和USB设备控制器用软核的形式集成在一块芯片上,微控制器我们是用14位指令字长度,且是单字节指令和单周期指令,其核心指令只有39条,容易掌握和设计,而且完全满足总体设计的要求。

2 MCU设备控制器工作原理及总体设计

整个设计的总体结构如图1所示,差分信号线D+和D-连接主机,接收时主机发送的串行数据通过收发器和USB设备控制器解码和校验等处理后存储到相应的RAM中;发送时由仲裁模块控制从RAM或ROM中提取相应数据经过USB设备控制器组合和收发器串行发送给主机。MCU主要协助USB控制器完成设备和主机之间的数据传输。

2.1 MCU的设计

MCU主要完成各种中断处理,而且协助控制器使主机检测和识别设备;设备刚插上PC时,MCU通过读取ROM中的指令来初始化专用功能寄存器,使能全局中断GIE和USB中断USBint,使控制器能及时响应各种USB中断;全局中断允许位GIE置位时,允许所有中断;清零时,禁止所有中断。当一个中断被响应时,GIE位被清零以禁止其它中断,并装载中断服务程序,将中断返回地址压入堆栈。引起装载中断服务程序的中断标志位在重新允许GIE之前通过软件清零,以避免重复响应中断。在中断服务程序中,通过检测中断标志位可以判断中断源,各中断标志位的置位不受GIE的影响;在设备与主机通信过程中,MCU处理setup包、in包、out包、ack、nak、stall包等的中断处理,我们规定了USB中断、定时器中断、外部中断、GPIO中断的中断入口地址分别为04H、08H、0CH、10H;MCU同时还对各功能寄存器进行相应的操作,比如写端点0的输入输出包允许的最大值,数据的触发位DSQ(即Data Toggle机制)等。

2.2 arbRAM、arbROM(仲裁模块)的设计

在设计中含有两种存储器:程序存储器(ROM)和数据存储器(SRAM),这两种存储器都有自己的总线,在一个时钟周期内,可以同时对两种存储器进行访问。USB和MCU都可以访问SRAM和ROM,仲裁模块就是为两者同时访问时不起冲突而设置的;USB访问ROM的地址空间100h-fffh(我们把设备的描述符存放在这里),且USB访问仅取14位宽的低8位数据。当USB与MCU同时访问ROM时,MCU优先。USB与MCU共享通用寄存器(SRAM),当USB的请求访问存储器信号到来时,USB访问存储器的地址信号的高三位不等于零时属于USB访问程序存储器的地址空间。当USB与MCU同时访问通用寄存器(SRAM)时,MCU具有优先权。

2.3 USB设备控制器的设计

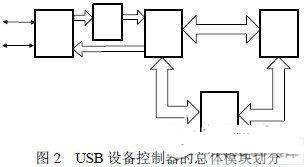

USB设备控制器是设计的重点部分,是本论文介绍的重点,总体的模块划分如图2所示;

2.3.1收发器的设计

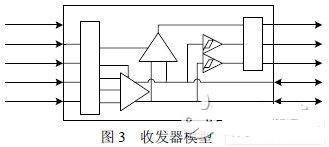

USB收发器作为USB接口的模拟前端主要把主机发送过来的模拟信号转换成数字信号VP、VM传到数字锁相环或把协议引擎发送过来的VP0、VM0数字信号转换成模拟信号,并完成串并和并串的转换;

收发器的模型如图3所示,Dplus为正相USB差分数据线,Dminu为负相USB差分数据线,两者都是双向的。OEn为USB发送使能,为低时作为发送功能,单相输出口被置为高阻,为高时作为接收功能,单相输入口被置为高阻。

2.3.2 Dpll(数字锁相环)模块

数字锁相环实现时钟恢复、分频及同步时钟;该模块用外部的6M时钟CLK进行分频,产生1.5M的USB系统时钟,以及把收发器产生的差分信号和并行信号进行锁相,避免产生亚稳态。

2.3.3 SIE(串行接口引擎)模块

SIE是USB控制器的主要模块;实现协议层的功能、信息包的解析和组合、同步信号识别、位填充和位剥离、NRZI(非归零反转)的编码和解码、同步字段和包结束码的检测和生成、CRC5、CRC16校验等功能;图4是设备接收主机发送数据时的状态机。

从图4可以看出设备在没有数据传输时处于空闲态,低速设备空闲时D+、D-处于J态,当有K态到来时进入状态转换;以KJKJKK为同步位,同步字段里的最后的2位是同步字段结束的记号,并且标志了包标识符(PID,Packet Identifier)的开始。然后根据不同的PID分别进入地址态或数据态,紧跟在地址态后面的是端点态,因为地址和端点分别是有7位和4位构成共11位,所以只要5位CRC校验就可以了,CRC校验完后就要结束此次的包传输,USB协议中以2个SE0态和一个J态来表示包的结束。在数据态判断是否为SE0态,SE0态表示8个字节的数据都发送完毕,因为非SE0态即J、K态都表示工作态,所以在数据态中如果总线上没有SE0到来就一直接收数据。

2.3.4 ENDPCTL(端点控制)模块

设计中用到两个端点,端点0和端点1.端点0是半双工传输,主要是在设备的枚举过程中用于控制传输,端点1是在枚举完成后的中断传输中用设备和主机之间的数据传输。由于中断传输主要是通过端点1输入,但也有少许输出(如键盘的LED灯输出),我们为了节省资源,所以由端点0完成少许的输出。

2.3.5 BUFCTL(缓冲器控制)模块

缓冲器控制模块是USB和SRAM及ROM的连接桥梁,在主机要求输入数据的IN token状态时,控制器从SRAM或ROM中取出数据送给主机或主机输出数据的OUT token状态时,控制器把接收到的数据存放在SRAM中,它主要根据串行接口引擎SIE的接收或发送准备信号来控制读写信号,保证数据能正确传输。USB与MCU共享通用寄存器区,usbREQUST为来自USB的请求访问存储器信号,usbADDR为USB访问存储器的地址信号,usbADDR[11:8]不等于零时属于USB访问程序存储器的地址空间。当USB与MCU同时访问数据存储器(SRAM)时,MCU具有优先权。

3系统验证环境

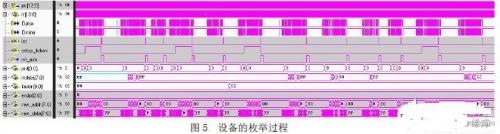

在完成了Verilog代码设计后,我们进行了仿真、综合验证,前仿用Modelsim、综合用Synplify Pro、综合后仿真用Cadence中的NC_Verilog,主要由于NC_Verilog在后仿中的速度要优于Modelsim,提高了效率;图5是用NC_Verilog仿真设备的枚举过程;

任何USB的数据传输都是建立在成功通过枚举的基础上的,只有正确完成了枚举,USB主机和设备之间的通信才正在建立起来。所以枚举是USB通信的最关键的一步。在验证过程中模拟了PC主机向设备发送各种命令来完成枚举。在图5中pid[3:0]中D、3、9、2、1、B分别表示Setup、DATA0、IN、Ack、Out、DATA1.当设备插上PC时主机会持续的SE0来复位设备,这时设备的地址默认为00,然后主机第一次发送Setup包来获取设备的前8个设备描述符,当设备成功返回数据后,主机第二次发送Setup包来给设备配置地址,从图中faddr[7:0]可以看出我们给设备配置的地址为02,在这以后主机都是通过这个地址向设备获取全部的18个设备描述符和全部的配置描述符集,在取完这些描述符后主机对设备进行配置,主机就识别出设备了。

4结论

本文描述了自主研发的MCU+USB设备控制器的设计思路。用Verilog语言对其进行了RTL级描述。用Modelsim进行前仿验证,并在Cadence公司的NC_Verilog上通过了综合后仿验证。为了进一步验证设计的正确性,本项目选择了XILINX公司的Virtex xc2s2006pq208芯片及XC18V02的存储器,并把上述IP核综合到此FPGA上加以验证。综合结果表明,协议层模块占用了1672个Slice(71%),652个Slice Registers(13%),2870个4 input LUTs(61%),51个bonded IOBs(36%)。使用上华工艺,该芯片已经流片返回了,并通过demo板连接到PC上,PC可以检测出为人体输入学设备,说明该芯片完全符合制定的设计要求。

评论