HyperLink编程和性能考量

摘要

HyperLink为两个KeyStone架构DSP之间提供了一种高速,低延迟,引脚数量少的通信接口。HyperLink的用户手册已经详细的对其进行了描述。本文主要是为HyperLink的编程提供了一些额外的补充信息。

同时本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些参数进行了讨论。

文章的最后附上对应本文的应用代码。

1、HyperLink介绍

HyperLink为两片DSP之间提供一种高速、低延迟,引脚数少的通信连接接口。

HyperLink的设计速度最高速率支持12.5Gbps,目前在大部分的KeyStone DSPs上,由于受限于SerDes和板级布线,速度接近为10Gbps.HyperLink是TI专有的外设接口。相对于用于高速Serdes接口的传统的8b10b编码方式,HyperLink减少了编码冗余,编码方式等效于8b9b.单片DSP为HyperLink提供4个SerDes通道,所以10Gbps的HyperLink理论吞吐率为10*4*(8/9)= 35.5Gbps= 4.44GB/s.

HyperLink使用了PCIE类似的内存映射机制,但它为多核DSP提供了一些更灵活的特性。本文将会使用几个范例来详细解释这一点。

本文还讨论了HyperLink的性能,提供了在各种操作条件下的性能测试数据。对影响HyperLink性能的一些因素进行了讨论。

2、HyperLink配置

本节提供了一些配置HyperLink模块的补充信息。

2.1 Serdes配置

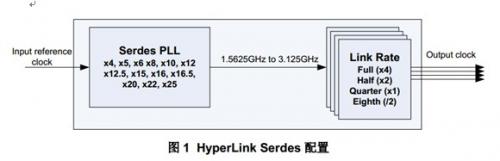

Serdes必须配置成期望的链接速度。图1表示了输入参考时钟和输出时钟之间的关系。

输入参考时钟建议限制在156.25MHz ~312.5MHz范围内。Serdes PLL的倍频系数必须合理配置生成的内部时钟(internal clock)限制在1.5625GHz ~ 3.125GHz范围内。

最后的链接速度由内部时钟(internal clock)驱动,通过link rate配置来得到。

2.2 HyperLink存储映射配置

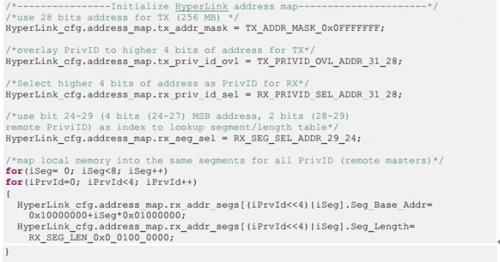

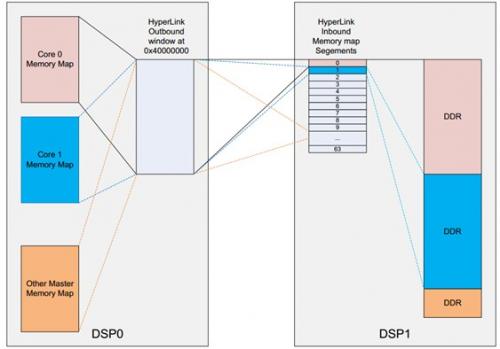

HyperLink的存储映射非常的灵活。HyperLink的用户手册对此作了详细的描述。本节将用两个例子来详细的解释它。图2是第一个例子。

图2通过HyperLink窗口映射到远端不同类型的存储空间

在这个例子里面,DSP1的存储空间映射到了DSP0的存储空间窗口0x40000000~0x50000000DSP0可以访问DSP1的所有内存空间,包括LL2,SL2,DDR,就像访问自己的本地的存储空间一样。在DSP0上,所有的Master都可以通过以0x40000000起始的Outbound窗口地址来访问DSP1的存储空间,但是不同master事实上可能访问到DSP1上不同的存储空间。原因是HyperLink发送侧传输数据时,会将PrivID一起传输。接受侧通过PrivID值,可以建立不同的地址映射表

对DSP0与DSP1的内存映射关系总结在下表(表1)。

通过上表的配置,可知当DSP0的core 0/1访问0x40800000,它事实上访问了DSP1上的LL2地址空间。

当DSP0的core0访问0x4D000000,它事实上访问了DSP1上DDR的地址空间0x8C000000当DSP0的core1访问0x4D000000,它事实上访问了DSP1上DDR的地址空间0x8F000000与本文档对应的范例工程将HyperLink配置成上述的内存映射关系。下面是关键部分的配置代码。

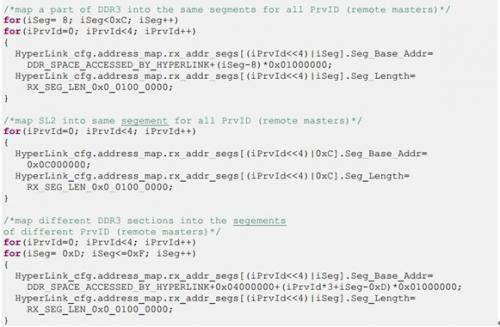

对于一些简单的应用,可能只是想访问远程DSP的DDR空间,那么下面的例子用于这种情况。存储映射关系如下图所示。

图3通过HyperLink窗口只映射到远端的DDR空间

这是最简单的例子,但是却可以访问远端DSP的大块存储空间。DSP0上的每个master(core或者其他外设)都可以可以访问DSP1上256MB DDR空间。下表描述了core0和core1的对remote DSP DDR存储映射。

3、HyperLink性能考虑

本节将让设计者对HyperLink访问远程存储空间的性能评估有基本的认识。同时提供了在不同的操作条件下获得的性能测试数据。大部分测试是在最理想的测试条件进行,以评估可以获得的最大吞吐量。

本文所描述的绝大部分性能数据是在C6670EVM上获得。C6670 EVM上DDR配置成64bit位宽1333M,HyperLink速率配置成10Gbit.

一些影响HyperLink访问性能的因素在本节中将会被讨论到。

3.1通过HyperLink实现存储拷贝的性能

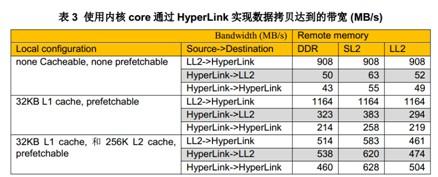

下表(表3)描述了使用HyperLink在LL2与远程大块线性存储空间进行数据传送测试获得的传输带宽。传输块的大小为64KB.带宽的计算是通过计算传输总的字节数除以传输所用的时间获得。

上述数据展示了cache能够极大的改善DSP内核通过HyperLink读取数据的性能。

但是L2 cache却遏制了通过HyperLink写数据的性能,这是因为L2是write-allocate cache.对于使能L2cache后的写操作,它总是会先从将要写入的存储区读取128字节的数据到L2cache,然后在L2 cache中修改数据,最后在cache冲突的时候回写回到原先的存储区,或者人为的回写回原存储区。

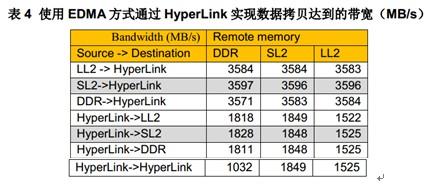

上述EDMA吞吐率数据是通过TC0 (传输控制器0)和CC0(通道控制器0)上测试得到,其他TCs的数据会比TC0稍低。整个传输的瓶颈是在HyperLink,不是在EDMA传输控制器上。

上述测试结果表明通过HyperLink进行写操作的性能会比通过HyperLink进行读操作的性能要好。

远程DSP存储空间类型不会对带宽造成明显的影响。访问远程DSP的SL2会比LL2快一些。

目前,通过HyperLink来访问远程DSP存储空间(相对其他接口)是具有最高的带宽性能的,但是访问远程存储空间比访问本地存储空间还是要慢。下表对比了访问本地LL2和DDR与远程DDR的吞吐性能。

大体来说,对本地存储空间的写入吞吐率是对远程空间进行写入操作的吞吐率的3倍。对远程空间的读性能会更差些。我们应该尽量避免远程读取数据。

3.2 DSP core通过HyperLink进行远程访问的延迟

DSP核通过HyperLink访问远程空间的性能高度依赖于cache.当DSP内核通过HyperLink来访问远程存储空间的时候,一个TR(传输请求)可能会被生成并传送给XMC(这取决于数据是否可以进入cache和被预取)。TR将会是下面中的一种。

一个单一的元素-如果存储空间不能被cache和预存取。

一个L1 cache line -如果存储空间可以进入cache,但是L2 cache没有被使能。

一个L2 cache line -如果存储空间可以进入cache,同时L2 cache被使能。

如果存储空间可以被预存取,预存取将会被使能为一个预存取的buffer slot.

如果L1/L2cache或者预存取命中,Hyperlink端口不会有数据传输

远程空间数据可以被本地L1 cache/L2 cache缓存,或者都没有被cache.如果对应存储空间的MAR(Memory Attribute Register)寄存器上的PC(Permit copy)位没有被置位,那么对应存储区的数据将不会进入cache.

如果MAR寄存器上PC位被置位,同时L2的cache空间是0(L2被全部配置成SRAM),那么外部存储空间的数据可以进入L1cache.

如果MAR寄存器上PC位被置位,L2的Cache空间大于0.那么外部存储空间的数据就可以进入L1cache和L2cache.

读取远程存储空间数据也可以使用XMC中的prefetch buffer.该特性可以在MAR寄存器PFX(PreFetchable eXternally)被置位后使能。

地址步进长度也会影响Cache和Prefetch buffer的使用效果。连续空间的访问可以最充分的利用cache和prefetch buffer,从而达到更好的性能。

以64bytes距离或者更大间隔进行步进访问将会导致每次L1 cache命中失败(miss),这是因为L1 cache line的大小是64byte.

以128bytes距离或者更大间隔进行步进访问将会导致每次L2 cache命中失败(miss)。

如果cache miss发生,那么DSP核就会被stall(等待数据)。Stall的时间长度等于传输延迟、传输间隔,数据返回时间,cache请求延迟的总和。

下面的章节描述DSP内核通过HyperLink访问存储区的延迟。测试伪代码如下列所示。

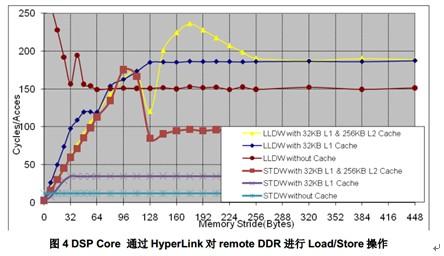

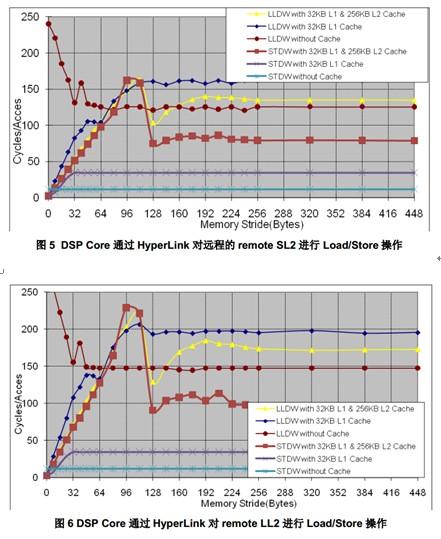

下图(图4)为1GHz C6670EVM上配置DDR 64bit 1333M测试获得的结果。通过HyperLink实现512次LDDW(load double word)或者STDW( store double word)操作的性能测试。图4绘制了各种测试条件下的性能。LDB/STB和LDW/STW和LDDW/STDW的指令周期数相同。虽然cache和prefetch buffer可以被独立配置,但是测试的时候使用的配置是:如果cache被使能,那么prefetch也被使能,如果cache没有被使能,那么prefetch也没有被使能。

Non-cachable写是post操作。所以它只会stall DSP core很短的一段时间。

但是read是non-post的,所以DSP内核会等待数据的到来,所以它会stall DSP内核相对长一点时间。

当cache被使能后,DSP core访问remote空间的吞吐性能高度依赖于cache.

地址的步进间隔也会影响到cache的使用。连续的地址访问可以充分的利用cache.但是地址的步进间隔超过case line的大小(L1 case line =64Byte,L2 Case line =128Byte)将会导致每次cache都无法命中,从而制约了性能。所以,对连续地址空间的数据访问(像大块数据拷贝),cache需要被使能,在其他情况下cache应当不要使能。

通过上面的图可以发现通过HyperLink访问DDR,SL2,LL2在性能上并没有明显的差异。所以,正常情况下,通过HyperLink来共享DDR是一个很好的选择,因为DDR容量大,而且成本低。

3.3 HyperLink传输使用DMA方式的开销(overhead)

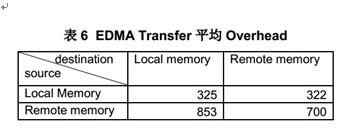

初始延迟被定义为EMDA事件触发到真实数据之间的传输开始之间的延迟。因为初始延迟很难被测量。所以我们就测试传输的开销,它被定义为传输最小单元数据的延迟。延迟的大小取决于源和目标端的类型。下表描述了使用EDMA在1GHz TCI6618EVM不同端口间传输一个字(word)时,从EDMA触发(写ESR)到EDMA传输结束(读IPR=1)的平均指令数目。

表6中,读Hyperlink的延迟是853个指令周期,写Hyperlink的延迟是322指令周期,因为写是post操作,而读是non-post操作。所以从HyperLink端口读取数据的延迟要高于写入数据到HyperLink.

对于小批量数据传送,传输开销(overhead)是很大的顾虑,尤其是系统中队列DMA阻塞的时候。单一元素的传送性能较差,延迟会占用大部分时间。所以,对于小批量数据传送,必须对使用EMDA方式还是DSP核方式来访问数据进行权衡。使用内核来访问单个随机数据的延迟会比DMA方式延迟小很多。本文3.2节已经做了详细的描述。

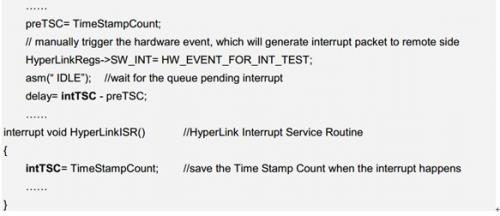

3.4 HyperLink中断延迟

一个DSP可以通过HyperLink来触发另外一个DSP的中断。通过HyperLink传递中断的延迟通过下列的伪代码获得测量。

测试是在Loopback模式下测试。

1GHz C6670的测试结果是大概710个DSP core cycles.

4、范例工程

本文的范例代码在C6670EVM上通过测试。EVM板子上有两个C6670 DSP,他们通过HyperLink互联。

在这个例子中,DSP1存储空间通过HyperLink被映射到了DSP0上。DSP0通过HyperLink窗口访问DSP1的存储空间就像访问自己的本地空间一样。这个工程范例也支持loopback模式。在loopback模式下,DSP0事实上是通过自己的HyperLink窗口访问了自己的本地地址空间。

本例也演示了通过HyperLink来实现中断传递。

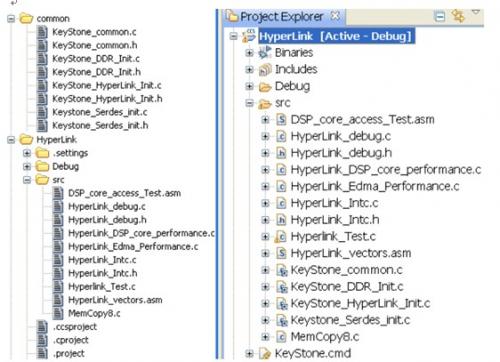

工程代码的目录结构如下图所示。

图7工程代码目录树

该示例代码同样可以在其他KeyStone DSP EVM板上运行。只是如果板子上只有一个DSP芯片,那么只能运行loopback模式。

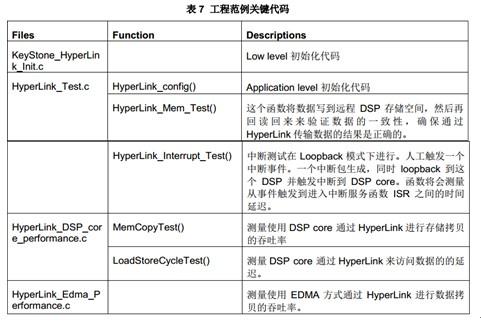

下表列出了KeyStone工程的关键代码列表。

运行这个范例工程的步骤:

1.连通CCS与DSP EVM.

2.下载代码到core 0 of DSP0.

3.下载代码到core 0 of DSP1.

4.先运行DSP1 ,然后运行DSP0. (如果EVM上只有一个DSP,且运行在loopback模式下,那么直接下载到DSP0,再运行)

5.检测每个DSP的stdout窗口,验证测试结果。

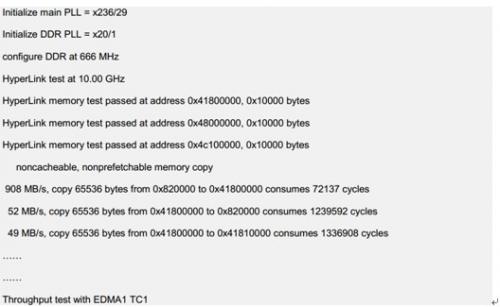

典型的输出信息如下:

用户可以在HyperLink_Test.c中的HyperLink_config()函数中修改初始化值,然后重新编译来验证在不同配置下的HyperLink性能。

这个例子是在CCS5.1下编译,使用pdk_c6618_1_0_0_5.如果在你的电脑上进行重新编译新的配置,你可能需要修改csl包含路径。

参考资料

1. KeyStone Architecture HyperLink User Guide (SPRUGW8)

2. TMS320C6670 datasheet (SPRS689)

评论