基于FPGA的网络图像采集处理系统设计

绍一种基于FPGA的网络图像采集处理系统设计,该系统采用单片FPGA,实现了图像的采集、压缩和网络传输功能,具有体积小,集成度高,算法升级灵活方便的特点。详述了模块的图像采集逻辑、RAM控制逻辑、压缩算法逻辑和网络传输功能的实现方法。测试结果表明,系统运行稳定,性能满足要求。本文介绍一种基于单片FPGA实现图像采集、处理和网络传输的设计方案。

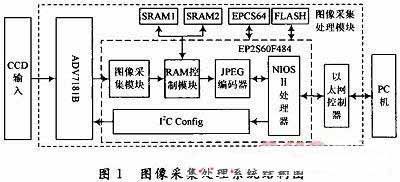

1 总体设计

总体框图如图1所示,系统采用Altera公司推出的StratixⅡ系列EP2S60F484型号FPGA作为图像采集处理和网络传输的核心,视频A/D采用ADV7181B芯片,支持PAL,NTSC和SECAM多种制式视频输入。图像采集处理在FPGA内部实现,主要有3部分,分别为图像采集模块、RAM控制模块和JPEG编码器。NiosⅡ处理器作为主处理器,主要是通过I2C模块对ADV7181B进行配置,控制JPEG编码器和实现图像的网络传输功能。

2 主要功能模块设计

2.1 图像采集模块

图像采集模块主要实现图像信号检测和图像裁剪的功能。

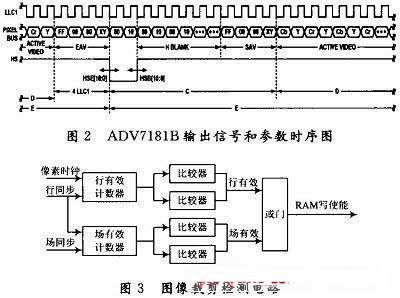

CCD摄像头输出的视频信号经过ADV7181B芯片解码,输出符合ITU-R BT.601标准的数据流。图2所示为ADV7181B输出的行同步信号参数和YCrCb信号时序图。当输出“FF 00 00 XY”时,表示有效图像数据的开始或者结束。其中XY[4]=0表示图像数据开始信号(SAV信号);XY[4]=1表示图像数据结束信号(EAV信号);XY[6]=0表示奇场信号;XY[6]=1表示偶场信号。通过检测EAV和SAV信号,分奇偶场提取有效的图像数据。

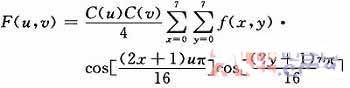

根据输出图像大小的不同要求,需要对图像进行裁剪。构造一个裁剪检测电路,如图3所示。利用像素时钟和水平同步信号、垂直同步信号进行计数,根据图像输出大小要求,设定比较器数值,当行列有效计数的数值在比较器设定的范围之内,检测电路使RAM处于写使能状态,把图像数据存入RAM。系统默认的图像输出大小是720×576像素,如果图像输出大小为512×512像素,那么行有效计数中的比较器数值分别为52和308,提取奇场和偶场中的第53行到第308行数据。同理,列有效计数中比较器分别为16和272。

2.2 RAM控制模块

RAM控制模块通过乒乓操作对图像数据进行缓存和读取,系统只存取图像的亮度信号,即Y信号。乒乓操作的处理流程如下:在第1场时间,将图像数据缓存到SRAM1;在第2场时间,将图像数据缓存到SRAM2,同时将SRAM1的数据送到JPEG编码器进行图像压缩;在第3场时间,将图像数据缓存到SRAM1,同时将SRAM2的数据送到JPEG编码器进行图像压缩,依此循环。将图像数据保存到SRAM时,由视频采集模块的行有效计数器和场有效计数器产生RAM写入地址。

由于图像数据是按照奇偶场先后传输的,为了得到一副完整的图像,需要将奇偶场数据合并。RAM控制模块先将奇场数据写入RAM奇数行中,即奇场第1行存在RAM的第1行,奇场第2行存在RAM的第3行,依此类推直到奇场288行数据全部存完为止;再将偶场数据写入RAM的偶数行中,即偶场第1行存在RAM的第2行,奇场第2行存在RAM的第4行,依此类推直到偶场288行数据全部存完为止。

2.3 JPEG编码器

JPEG编码器是图像压缩算法实现的核心,JPEG编码器主要有5部分,分别是二维离散余弦变换(2D-DCT)、量化、Z型扫描、游程/预测编码、霍夫曼编码。如图4所示原理框图。输入是图像原始的亮度Y数据,最后经过霍夫曼编码器输出码流。

2.3.1 2D-DCT实现

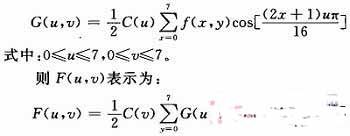

对于8×8图像块的二维DCT的变换公式为:

式中:0≤u≤7,0≤u≤7,f(x,y)为对应像素点的像素值;F(u,v)为变换后的DCT数值。根据余弦的正交性,可将上式分解为一维DCT变换。设:

式中:0≤u≤7,0≤v≤7。

因此二维DCT变换可以转换为2个一维DCT变换。目前比较常用的变换方法有2种:一种是直接法,通过将8×8图像数组进行多项式转换或者三角分解进行二维变换;或者另一种是间接法,将8×8图像数据先按行进行一维DCT变换,然后再对变换结果按列进行第2次一维DCT变换,进而可以得到二维DCT变换结果。前者需要的乘法器较多,而且实现步骤较繁琐,后者在这两方面上拥有很大的优势,能够形成快速DCT变换,更适合FPGA硬件的实现,因此采用后者方法实现。

目前比较成熟的一维DCT算法主要有Chen算法、Loeffler算法、Lee-Huang算法、ANN算法等,每种算法所需要的乘法次数和加法次数各不相同,表1所示为几种常用算法的比较。根据算法的复杂度和硬件计算速度,本文采用Loeffler算法。

Loeffler是一种基于行列分解的快速一维DCT算法,适合FPGA硬件实现。采用Loeffler算法实现一个8点的一维DCT变换,只需要11次乘法运算和29次加法运算。硬件实现算法的结构图如图5和图6所示。

2.3.2 量化和编码

量化是将经过DCT变化后的系数值除以量化表中的量化值,其结果四舍五入得到。系统采用推荐的亮度量化表对图像数据进行量化,该表存在FPGA的片上RAM中。由于硬件除法是通过迭代减法完成的,速度慢,因此先计算量化表中数值的倒数值,把DCT变化系数乘以量化表对应的倒数值,即可将除法转换成速度较快的乘法运算。

量化后系数经过Z型扫描器转换成一维ZIG-ZAG序列,序列的第1个数值表示直流(DC)分量,其后的63个数值表示交流(AC)分量。对DC分量采用一维差分前值预测编码,即将DC分量减去上一个8×8子快的DC分量。对AC分量采用游程编码,并且用一个字节的高四位来表示AC分量连续0值个数,低四位表示下一个非零系数所需位数,这样能够表示的最大0值个数为15个,如果AC分量中0值个数多于15个,采用(15,0)来表示。(0,0)表示EOB,说明后面分量值全为0。这样游程/预测编码对系数0的值进行压缩。最后霍夫曼编码器利用霍夫曼表分别对DC和AC系数进行霍夫曼编码,输出JPEG图像码流。

2.4 网络传输

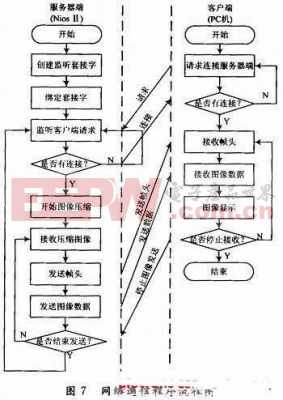

通过在NiosⅡ处理器上移植支持TCP/IP协议栈的μC/OS-Ⅱ操作系统来实现图像的网络传输功能。软件流程图如图7所示。

首先将NiosⅡ作为网络通信服务器,创建一个网络监听套接字,将该套接字同NiosⅡ处理器的本机的IP地址和端口号进行绑定,调用Listen监听函数使系统处于监听状态,监听客户端(PC机)请求,一旦监听到客户端的连接请求,服务器端置图像压缩使能端有效,开始图像的压缩,并接收硬件逻辑完成压缩的图像数据,然后服务器端向客户端发送图像的帧头和图像数据,一帧图像发送完成后会接着发送下一帧图像,直到收到停止图像发送指令,进入下一个监听的等待状态为止。客户端主要是向服务器端发出连接请求,一旦连接成功,即开始接收服务器端传送的图像帧头和图像数据,并将图像进行显示。客户端在停止接收图像前,会不断重复接收图像数据的工作过程。

3 测试结果

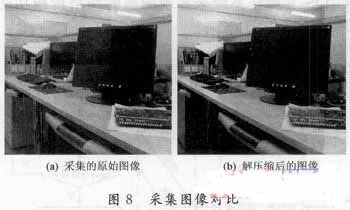

AD采集一副大小为720×576的图像,经过硬件逻辑裁剪成如图8(a)所示的512×512大小的图像,由JPEG编码器进行图像压缩,在PC机上解压缩后的图像如图8(b)所示。将原始图像和解压缩后的图像进行对比,计算图像的峰值信噪比:

式中:MSE为原始图像和压缩图像的均方误差。从图中可看到,PSNR>30时,图像视觉失真度比较低。

4 结语

本文介绍了一种基于FPGA的网络图像处理系统设计和实现方法。系统主要包括图像采集模块、RAM控制模块、JPEG编码器3部分逻辑。在单片FPGA上实现图像的采集、裁剪、缓存和JPEG编码,构建NiosⅡ处理器实现图像的网络传输功能。测试表明,系统的体积小,功耗低,算法升级灵活方便。此外系统运行稳定,性能也满足要求。

评论