GPS信号中断时惯导芯片的位置信息感知系统设计

引言

当今社会,GPS卫星定位系统早已广泛应用于人们的社会生活中,如交通工具导航、个人定位服务等。但在某些情况下,由于物体遮蔽、散射等原因,我们无法实时接收到GPS卫星信号(比如列车进入隧道)。所以有必要研究在GPS信息缺失的情况下,如何通过一定的算法产生模拟GPS信息,从而实现全天候的无缝位置感知。这在某些对位置信息敏感的场合中就显得非常急迫和重要。

1 惯导芯片简介

ADIS16003是ADI公司的一款低成本、低功耗,具有SPI接口的双轴加速度计,属MEMS传感器件。它可以测量动态和静态加速度并以数字量输出,测量范围最小可以达到±1.7 g,同时还集成了温度传感器,可用于惯性导航、振动检测和稳定性测试等场合中。

SPI是串行外围设备接口,是Motorola公司首先在其MC68HCXX系列处理器上定义的。目前已广泛应用在EEPROM、Flash、实时时钟、A/D转换器以及数字信号处理器和数字信号解码器之间,是一种高速的全双工同步通信总线。SPI通信只需要4根线,分别为SDI(数据输入)、SDO(数据输出)、SCK(时钟)和CS(片选)。通信是通过数据交换的方式完成的。SPI接口使用串行通信协议,由SCK提供时钟脉冲,SDI、SDO则基于此脉冲完成数据传输。数据输出通过SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取,完成一位数据传输。数据输入也使用同样的原理。

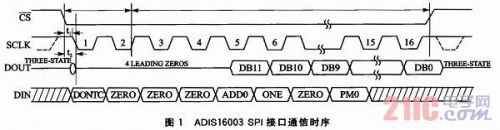

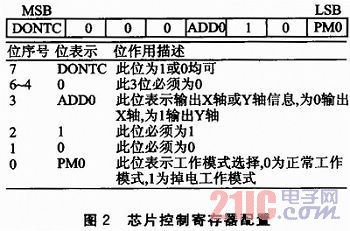

ADIS16003的SPI接口通信时序及控制寄存器配置如图1、图2所示。其中,常用控制字为00000100和00001100,分别表示以正常模式采集X轴和Y轴双轴轴向加速度。

2 系统工作原理及主要控制信号说明

本文研究了如何在移动端GPS信息缺失的情况下,使用SPI协议建立FPGA与惯导芯片ADIS16003之间的通信,从而获取移动物体当前的加速度。DSP将通过EMIF接口读取此加速度,并根据之前有效的GPS信息推算出当前的概略GPS信息(经纬度、速度和时间等)。

2.1 工作原理

FPGA驱动ADIS16003惯导芯片工作包括初始启动和正常启动两种模式。

(1)初始启动模式

FPGA上电复位时自启动ADIS16003芯片,配置ADIS16003控制寄存器,并读取芯片测得的双轴轴向加速度初始值,存储到EMIF接口的0x068~0x069地址空间供DSP读取,用作误差校正之用(此模式工作在移动端处于静止状态时,且此模式仅由DSP读取1次)。

(2)正常启动模式

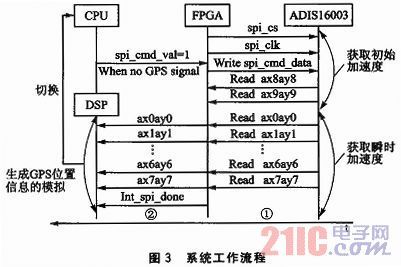

初始启动模式完成之后,FPGA将自动转入数据采集阶段,源源不断地通过SPI接口从ADIS16003芯片中采集双轴轴向瞬时加速度,以备DSP使用。加速度每秒采集8次,每隔0.125 s采集一次。每秒都将得到8组结果,分别为ax0ay0、ax1ay1、ay2ay2、ax3ay3、ax4ay4、ax5ay5、ax6ay6和ax7ay7,存储于FGPA内部的8个中间寄存器单元reg0~reg7(非EMIF接口,每个输出结果为12×2位,存储于32位的寄存器组中),并随着时间的推移不断地刷新。这么做的目的是确保这8个寄存器组中始终保存有最近1 s的移动物体加速度信息,以保证加速度信息的准确性和有效性。当CPU通过GPS接收天线检测到GPS信息丢失时,CPU通过PCI接口给FPGA配入spi_cmd_val信号(高电平有效),同时通过HPI接口给DSP写入信息丢失前2 s的GPS信息(包括经纬度、速度和时间),作为定位基点。FPGA检测到spi_cmd_val信号有效后,立即将中间寄存器单元reg0~reg7中存储的瞬时加速度送入EMIF接口的0x060~0x067地址单元(32位),同时拉高int_spi_done信号,产生外部中断(拉低DSP的引脚)通知DSP从EMIF接口读取加速度信息,并通过后续软件算法进行信号处理,转化为移动端经纬度信息。再通过DSP的HPI接口上报给CPU,从而使高层获取移动端当前GPS信息,即完成了GPS位置信息的模拟。加速度存储格式如表1所列。其中包括初始和瞬时加速度值,共占用32位EMIF接口10个地址单元。

2.2 主要控制信号说明

①spi_cmd_data:ADIS16003芯片控制字(寄存器),8位,FPGA配入。

②spi_cmd_val:GPS信号缺失时ADIS16003启动信号,CPU发出,脉冲触发。

③spi_cmd_val_reg:ADIS16003启动信号寄存器,及时存储触发脉冲,持续一个时钟后清0。

④spi_data_i:ADIS16003串行输出信号,包括双轴轴向加速度,每个spi_clk时钟下降沿输出一位,16个时钟周期完成一次运算。

⑤spi_cs:SPI片选信号,低电平有效。

⑥spi_clk:SPI通信时钟信号,由主时钟分频得到,此处进行32分频。

⑦spi_data_o:ADIS16003控制字输入信号,8位串行输出,spi_clk时钟上升沿动作。

⑧spi_rdata:ADIS16003运算结果,12位,每个spi_clk下降沿输出一位,采取移位拼接方式(向左移),在第16个时钟下降沿输出一次完整的采集结果(每次采集至少需要16个时钟周期)。

⑨spi_state:SPI工作状态信号,0为IDLE,1为BUSY,2为DONE,采用有限状态机进行设计。

⑩spi_wr_cnt_o、spi_wr_cnt_i:十六进制计数器,时钟上升沿和下降沿分别计数。

整个系统工作流程如图3所示。

2.3 DSP后续软件处理流程

DSP后续软件处理流程如图4所示。DSP在CCS 3.3软件环境下计算完成。此处的基点(basepoint)是指最接近GPS信号消失前的具有有效GPS信息的移动物体位置,即GPS消失前2 s的移动端GPS信息(每秒测量1次)。角度计算是指DSP将距离信息转换为GPS经纬度信息。

3 程序实现及功能仿真

3.1 芯片资源

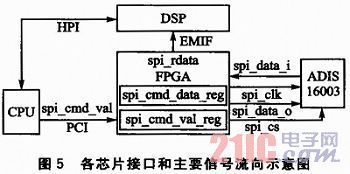

本系统采用的FPGA芯片为Cyclone III系列的EP3C120F80C7器件,DSP芯片为TMS320VC5510,惯导芯片采用ADIS16003。各芯片接口和主要信号流向示意图如图5所示,包括PCI、SPI、EMIF和HPI等主要外设接口。

3.2 软件功能仿真

本系统的底层SPI通信部分使用FPGA进行驱动,采用Verilog HDL语言编写程序,并在Quartus 10.1集成环境下进行功能仿真验证,如图6所示。结果显示,数据采集符合设计逻辑,当所有数据采集完成一次之后立即送出中断信号触发DSP读取。

4 测试结果

利用Signal Tap II Logic Analyzer在线逻辑分析仪进行板上硬件实际调试,图7为SignalTap加速度在线采集实测波形。测试结果显示数据采集和处理符合芯片时序要求;FPGA与DSP的EMIF接口配合良好,经过后续DSP软件算法处理后能成功推算出移动物体当前的GPS信息,及时上报CPU(每秒1 s)。其中SPI总线通信时钟为1.4 MHz。经过测试,系统完全能够达到设计要求,已在某大型通信系统中得到应用。

结语

通过本系统的设计和调试过程可以看出,使用FPGA作为物理层驱动具有SPI接口的数字芯片是简单而有效的一种数字设计方案,可以较容易地满足芯片的时序要求。通过与EMIF接口的配合还可以很好地利用DSP芯片完成众多嵌入式系统的设计。

评论