改善PLD性能的简易方法及

改善PLD性能的简易方法及电路

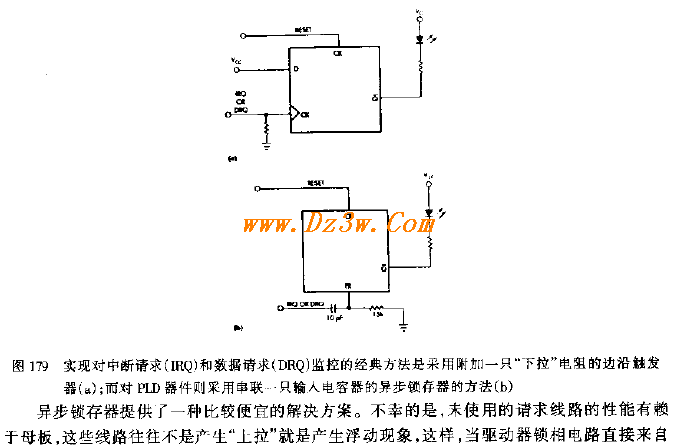

在ISA总线上要查找中断和DMA请求,如果没有合适的工具,那将是十分麻烦和费时的。一只数字存储示波器或逻辑分析仪当然能胜任此项工作,但是,为了监视缓冲中断或数据请求线路, LED 通常要求质量很好才成。按照ISA总线规范,在这些线路上从低到高的传输要求有一个请求。因此,监视器应该包含为每一线路进行边沿触发的触发器(见图 179a ) ,这种布局适用于SSI逻辑,但不适用于具有共时钟的PLD。为使用 PLD ,你需要一个能够为每一个请求线路检测低到高顺序的同步状态机。这样的电路就会要求每个通道有二个触发器或每个GAL20V8有4个通道。

总线时,你就可能得到假读出,而直到手动重新启动之前,你只需在上升沿时触发锁相电路并保持LED的接通就会产生这种情况。采用电容器是个好方法,因为与 GAL 输人和下拉电阻器串联的电容器,能一块组成简单的高通滤波器(见图 179b ) ,正边沿能预调锁相电路, GAL 的内置二极管能籍制信号任何负的过冲,结果每只GAL20V8可得到 8 个通道。

评论