CPLD是什么?

1.何谓CPLD

由于信息工业发展讯速,从一般人之日常生活就可见一般;小至每个人手上的行动电话、家家户户皆有之洗衣机、停车场的全自动化,大到银行里的数据库、飞机上的自动驾驶,无一不是计算机所及的地方,而不论是计算机本身亦或其外围之,皆为数字电路之产物。

对于大部份学习数字电路设计的人来说,其学习过程大抵从最简单的组合逻辑电路设计开始,接着便是顺序逻辑、简易之模块设计、至比较复杂完整之系统设计。

传统的实验方式,每做一个实验就必须重组一个硬件线路,特别是复杂的线路,相当费时耗力且不易进行,因此也就常省略跳过,导致缺乏设计架构稍大且完整的电路的经验。

为了改进以往数字电路学习方式的缺点,并且缩短开发大型数字电路的时间,所以有了整合式数字电路设计环境的发展,此种环境是以个人计算机为平台,配合电子设计自动化(EDA)软件的执行,达到从电路设计输入、仿真、下载验证、修改、烧录一气呵成,而且也让自行设计开发逻辑芯片的梦想得以实现。

是何因素促成数字电路学习的方式改变呢?究其原因首推可程序逻辑组件(PLD)的快速发展。逻辑芯片大致上分成标准逻辑芯片(Standard Logic)与应用规格芯片(ASIC)两类;而PLD为ASIC之一种。

PLD由小而大分为以下几种:小型/简单型PLD(Simple PLD)、复杂型CPLD(Complex PLD)、场可规划型门阵列(FPGA)。

CPLD是较复杂的逻辑组件,它整合了更多的PLD逻辑方块及相互关系联机架构,芯片内含多个类似PAL的方块及可程序化之绕线。

2.CPLD架构区分

分为EEPROM(Flash)架构和SRAM架构:

EEPROM架构密度小,多用于5,000门以下的小规模设计,适合做复杂的组合逻辑,如:编码器。

SRAM架构的CPLD(FPGA),密度高,缓存器多,多用于10,000闸以上的大型设计,适合做复杂的时序逻辑,如数字信号处理及各种算法等。

三、CPLD基本结构

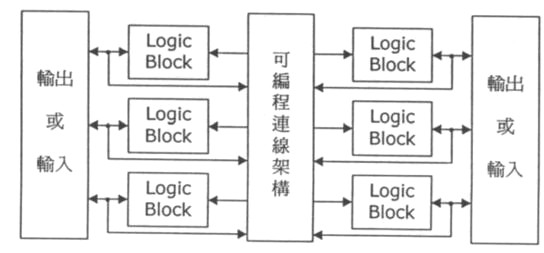

CPLD 是Complex PLD 的简称,顾名思义,其系一种较PLD 为复杂的逻辑组件。CPLD 是一种整合性较高的逻辑组件。由于具有高整合性的特点,故其有性能提升,可靠性增加,PCB 面积减少及成本下降等优点。CPLD 组件,基本上是由许多个逻辑方块(Logic Blocks)所组合而成的。而各个逻辑方块均相似于一个简单的PLD 组件(如22V10)。逻辑方块间的相互关系则由可编程的连线架构,将整个逻辑电路合成而成。CPLD 的架构方块图,如下

图(一)所示。

图一、CPLD 之架构方块图

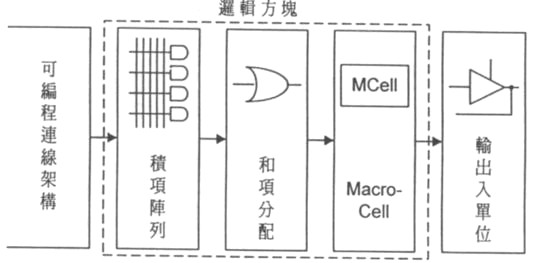

每一个逻辑方块(Logic Block)内的内部示意图,则如下图(二)所示。

图二、逻辑方块(Logic Block)内部之架构示意图

常见的CPLD 组件有Altera 公司的Max 5000 及Max 7000 系列、Cypress 的Max 340 及Flash 370 系列...等,一般来说CPLD 组件的可逻辑门数(gate count)约在1000~7000 Gate之间。

因此目前在CPLD装置的发展上,通常都是怎么选用的,是否会觉得:CPLD(Complex Programmable Logic Device;复杂可程序逻辑装置)在整个PLD领域中,似乎有点像是个演进历程的步阶性产品,比CPLD简易的有SPLD(Simple Programmable Logic Device;简易可程序逻辑装置),而比CPLD复杂的则有FPGA(Field Programmable Gate Array;现场可程序逻辑数组)。在诸多特性表现上CPLD也都是介于SPLD与FPGA间,如逻辑资源密度、功耗用电、封装大小与引脚数目、以及价格等,因此也认为,CPLD面临「高不成、低不就的夹心危机」。

评论