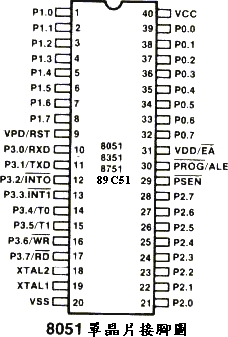

8051的引脚说明

8051/8751/8031为40支引脚的DIP包装芯片。一如INTEL公司其它的CPU芯片一样,8051芯片也有许多引脚是多用途的。在此将说明每一支引脚的信号名称及其功能用途。信号名称后面括号中的数字代表其引脚号码。

Vss(20)-接地(GND)电源信号。

Vcc(40)-+5V电源输入端。

8051的引脚说明用途

XTAL1(19), XTAL2(18)-工作频率输入信号。若使用石英振荡晶体时,则应将石英晶体的两支引脚接到XTAL1与XTAL2引脚上。若使用外部的脉波信号源时波信号应接至XTALl引脚上,而XTAL2则必须接地。可使用的工作频率范围为:1.2 ~ l2 MHz。

RST/VST(9)-硬体重置(Reset)输入信号。当本引脚收到一个由low上升为high的转态信号时,8051将被重置,此时8051将其内部的特殊功能暂存器(Special Function Register, SFR)设定为预设值,并由地址0000H开始执行程序。本引脚(VPD)亦可用于8051的功率下降(Power Down)模式,当VPD维持约+5V而Vcc低于规定的+5V+5%时,VPD将供应电源(称之为Standby Power)给其内部的RAM使用,以保存其资料。

/EA(31)-外部存取允许(External Access Enable)输入信号。决定程序记忆体最前面bytes(0000H-0FFFH)是来自芯片内部的ROM/EPROM (/EA=1),或来自外部的ROM/EPROM (/EA=0)。注意:由于8031芯片无内部的ROM/EPROM,故803l的/EA必须接地(即低电位信号)。

P0.0~P0.7(39~32)-接口0。本引脚有两种用途:当作I/O口时为口0,为8位元双向开吸极(Open Drain)的I/O口。将信号l写入口0时,可使其引脚进入高阻抗状态,此时可当作I/O输入引脚。每支引脚可驱动8个LS-TTL负载。本引脚亦当作多工式的低阶地址(A0-A7)及资料(DO-D7)汇流排,可供存取外部的记忆体。通常在每一个指令周期中先送出低阶地址信号(此时亦伴随着送出ALE信号),然后再送出资料信号,故这8支引脚又称之为AD0 - AD7。

P1.0~P1.7(1~8)-接口1。为8位元双方向性的I/O口。将信号l写入口l时,可使其引脚由其内部提升为高电位状态,此时可当作I/O输入引脚。每支引脚可驱动4个LS-TTL负载。在8052系列芯片中,P1.0及P1.1可做如下之用途: T2(P1.0):计时器/计数器2外部信号输入端。 T2EX(P1.1):计时器/计数器2在捕捉(Capture)模式时的触发/重新载入信号输入端。

P2.0~P2.7(21~28)-接口2。本引脚有两种用途:当作I/O口时为8位元双向I/O口。将信号1写入口2时,可使其引脚由其内部提升为高电位状态,此时可当作I/O输入引脚。每支引脚可驱动4个LS TTL负载。本引脚亦当作高阶地址(A8-A15)汇流排,以存取外部记忆体。

P3.0~P3.7(10~17)-接口3。为8位元双方向性的I/O口。将信号1写入口3时,可使其引脚由其内部提升为高电位状态,此时可当作I/O输入引脚。每支引脚可驱动4个LS-TTL负载。本引脚亦可使用于下列之用途:RXD(P3.0):串列口信号输入端。 TXD(P3.1):串列口信号输出端。 /INT0(P3.2):外部中断0信号输入端。 /INT1(P3.3):外部中断l信号输入端。 T0(P3.4):计时器/计数器0外部信号输入端。 T1(P3.5):计时器/计数器l外部信号输入端。 /WR(P3.6):外部资料记忆体写入闪控(Strobe)信号输出。 /RD(P3.7):外部资料记忆体读取闪控(Strobe)信号输出。

/PSEN(29)-程序储存允许(Program Store ENable)闪控输出信号。在外部程序记忆体的指令码撷取周期时,/PSEN将送出一个闪控信号,以表示CPU正自外部的程序记忆体中读取指令码。

ALE(30)-地址锁存允许(Address Latch Enable)输出信号。当CPU自外界记忆体中撷取指令码或存取资料时,ALE将会在一个汇流排周期(Bus Cycle)开始时送出H的信号,表示P0.0-P0.7(AD0-AD7)正送出低阶地址A0-A7信号,以供外界电路锁定这些低阶地址信号。由于ALE信号频率固定为振荡器工作频率的1/6,故ALE信号也可当作脉波信号源。

I/O口的结构和使用法

8051里的四个I/O都是双向,且每个口都有锁存器(在特殊通能暂存器里的P0至P3),输出驱动器,和输入缓冲器。 P0和P2的输出驱动器,和P0的输入缓冲器可用来存取外部记忆体的资料,在这种应用下,P0输出外部记忆体地址的低位元组,且使用时间多工的方式作为资料的写出与读入口。当外部记忆体地址为16位元宽时,地址的高位元组由P2输出。否则P2的引脚就一直输出SFR内P2暂存器的内容。

图中画出了P1、P2、P3三个I/O接口里的每一只脚的内部等效电路图的功能图。位元锁存器(再SFR中的一个位元)以一个典型的D型正反器代表,再CPU送出写入锁存器的信号时,它会将内部汇流排的信号锁住。再CPU送出读入锁存器信号时,正反器的Q输出段的信号会放入内部汇流排而被CPU读入。当CPU送出读入引脚信号时,I/O接口的引脚信号会被读入CPU。

接口1,2和3都有内部提升电阻(不一定是电阻),接口0则为漏极开路(Open drain)输出。而每一个I/O引脚都可以当作输入或输出使用(接口0和接口2当作地址/资料汇流排使用时,不能当作一般I/O使用)。当作输入时,I/O的位元锁存器的内容必须为1,这个1会将驱动输出的FET关掉,因此引脚(1、2和3)的信好就被内部的提升电阻至高电位,但可以由外部电路将它拉至低电位。

接口0内部则没有上拉电阻。在PO上的输出驱使上拉(pull-up) FET只有在外部记忆体存取时使用到,其它时间上拉用FET则处在关掉的状态。因此PO被当成输出时是为开泄极的型态,若写入1到单元闩器时会使得两个FET都关掉,此时引脚就呈浮接状态。在此状态下可将它当作高阻抗输入使用。

评论