可编程逻辑实验板的设计与制作

一、实验板电路原理分析

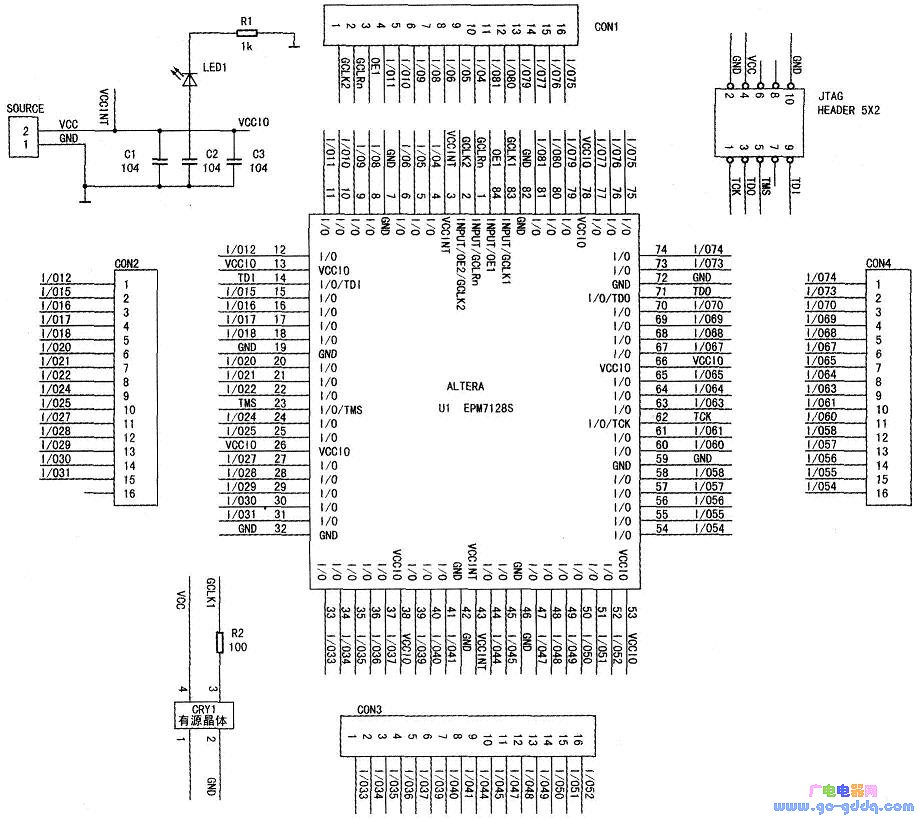

在本制作中,CPLD芯片采用EPM7128SLC84-15(ALTERA公司的MAX7000系列产品),该芯片具有高阻抗、电可擦等特点,可用门单元2500个,有68个I/O引脚、8个逻辑阵列块、128个宏单元,管脚间最大延迟为5ns,工作电压+5V,封装形势为PLCC-84。该实验板的电路如下图所示。

下图中相同标号的线是连接在一起的。Ul为可编程逻辑器件EPM7128S。使用时注意:VCCIO:设置I/O口电压端,可以接3.3V或SV,如果接5V则I/O的输入输出电压为5V,本制作中接5V,在与3.3V系统连接时接3.3V;VCCINT:设置内部操作和缓冲器电压,设置为5v。GCLK:全局时钟脚,此脚的驱动能力最强,到所有逻辑单元的延时基本相同,所以如果系统有外部时钟输入,建议定义此脚为时钟脚;OEl:全局输出使能,如有三态输出,建议由此脚来控制(也可由内部逻辑产生输出使能信号);GCLRn:全局清零,如有寄存器清零,建议由此脚来控制(也可由内部逻辑产生清零信号);OE2/GCLK2:全局输出使能/全局时钟脚。

SOURE端为+5V的电源端口,在制作时可采用φ4.5的插座或其他方便与身边的+5V电源连接的接口。CON1、CON2、CON3、CON4为可编程逻辑器件I/O口的引出端口,在制作时采用单排针,以便灵活使用外围I/O口设计自己的电路。JTAG接口为5×2的10芯插座,方便与Altera标准的ByteBlasterMV下载线连接。为了做时序电路实验,在板上使用了一个20MHz的有源晶振,用户也可根据自己的需要更换晶振的频率值。

使用有源晶振应注意:有个点标记的为①脚,按逆时针方向(管脚向下)依次为②、③、④脚。其通常的定义为:①脚悬空,②脚接地,③脚接输出,④脚接电源电压。

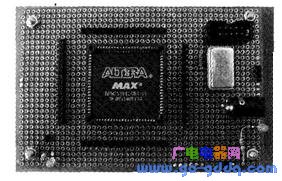

焊接时,先选一块质量较好的单孔板,在上面规划好各元件和接口插座的布局,然后开始焊接。EPM7128S放在PLCC-84插座上,芯片缺口对准插座缺口,PLCC-84插座引脚排列如右图所示。

晶振应尽可能靠近GCLK脚。在板上的+5V走线与地之间应在一定的距离,并接一只104的退耦电容。

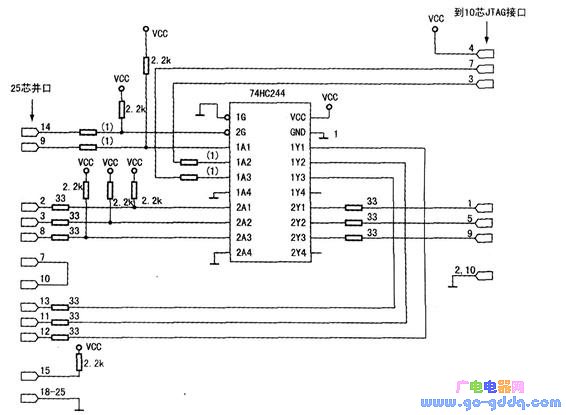

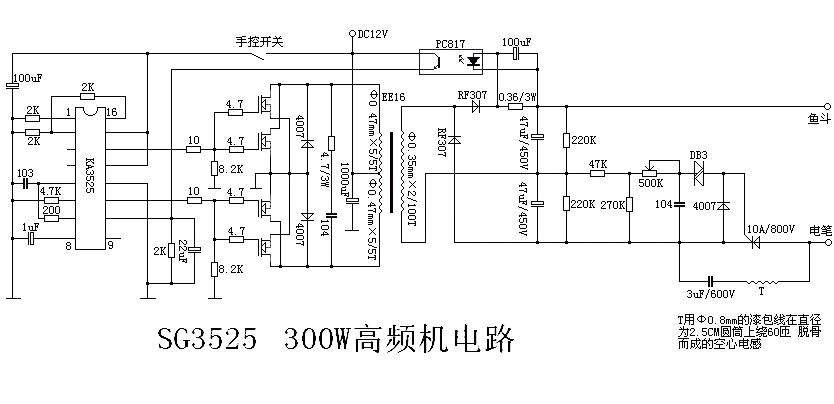

三、下载线的制作

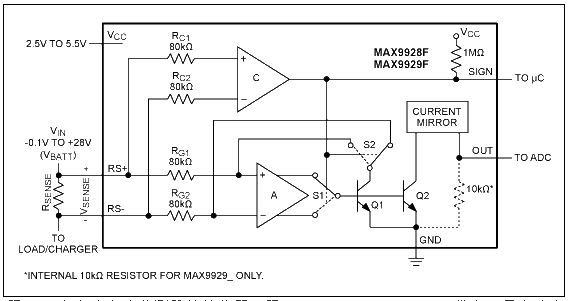

EPM7128的下载线为ByteBlasterMV并口下载线,可以对MAX9000MAX7000SMAX7000B、MAX7000A、MAX3000系列器件进行下载。也可以配置APEX20K,FLEX10K(包含FLEX10KAandFLEX10KE),、FLEX8000和FLEX6000器件。下图为Altera提供的ByteBlasterMV下载线电路图。

四、实验板的使用方法与实例

右图为该实验板的实物图。如想进一步降低成本,可以使用ATF1508替代EPM7182S,其性能及引脚定义与EPM7128完全一样,可以直接代换,只是在下载程序时,要转换下载文件的格式,再通过ATMEL的下载工具下载。

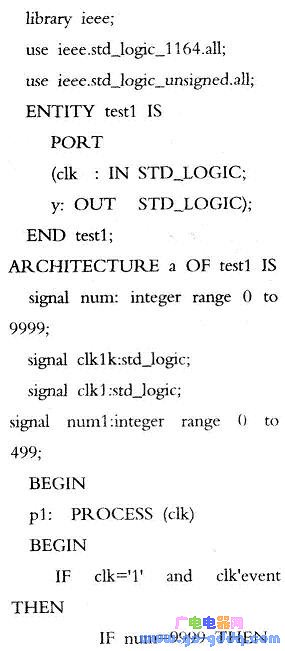

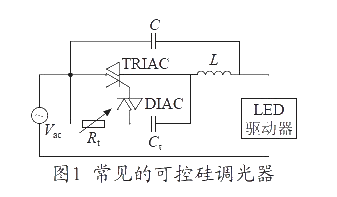

由于此实验板将可用的I/O口都通过排针引出,所以使用时配上自己的外围电路可以完成很多开发设计。如计数器、分频器、数码管的动态扫描显示、加法器、乘法器、秒表等实验。通过设计一个将晶振产生的20MHz信号分频为1Hz信号的电路,来说明实验板的用法和EDA设计自顶向下的流程。在编程之前将欲输出1Hz的管脚接上电阻和LED到地,以便观察。用QUARTusII6.0软件。FPGA/CPLD设计的流程是:设计的输入(原理图输入或硬件描述语言输入,这里使用VHDL语言输入)、综合、适配、功能仿真与时序仿真、下载或配置。

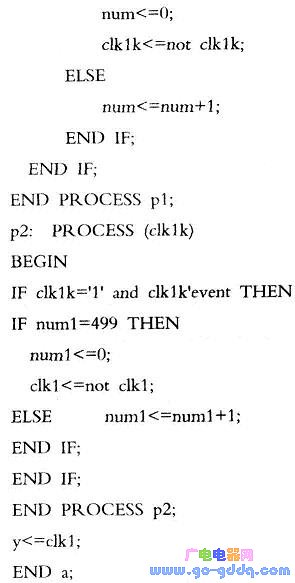

首先,打开QuartusII,点击“新建”→“VHDL”,此分频器的VHDL语言程序如下:

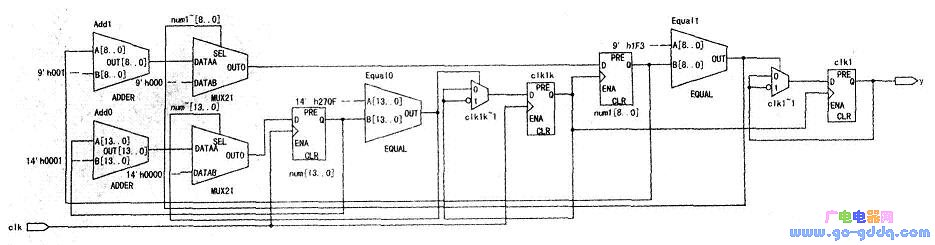

保存时,注意文件名与实体名一样。系统提示是否新建工程,点击是,然后点击下一步,一直到选择器件,选中MAX7000S系列的EPM7128SLC84-15,点击下一步到结束。接着点击“Processing”→“Analyzecurrentfile”,通过后点击“Tools”→“netlistviewers”→“RTLviewer”,就可以看到如下图所示的综合后的电路了。

接下来,可以建立波形文件仿真,通过后再锁定管脚,将输入20MHz的脚锁定到GCLK1,输出1Hz的脚锁定到焊接有LED的脚,然后再点击Processing→startcomplICation,全部通过后就可以点击Tools→programer进入下载界面,点击Hardwaresetup选择ByteBlaster[LPTl],mode选择JTAG,将下载线一头插pC机的25针并口,另一头插入实验板上,然后在点击Start,下载成功后就可以观察到LED的闪烁。

此实验板将可用的I/O口都通过排针引出,具有可移植性和可扩展性。

使用时配上自己的外围电路可以完成很多实验及开发设计。

评论